老外总结:高频PCB布线经验

因为接地平面通常具有很大的表面积和横截面积,所以使接地平面的电阻保持最小值。在低频段,电流会选择电阻最小的路径,但是在高频段,电流会选择阻抗最小的路径。

然而也有例外,有时候小的接地平面会更好。如果将接地平面从输入或者输出焊盘下挪开,高速运算放大器会更好地工作。因为在输入端的接地平面引入的寄生电容,增加了运算放大器的输入电容,减小了相位裕量,从而造成不稳定性。正如在寄生效应一节的讨论中所看到的,运算放大器输入端1 pF的电容能引起很明显的尖脉冲。输出端的容性负载——包括寄生的容性负载——造成了反馈环路中的极点。这会降低相位裕量并造成电路变得不稳定。

如果有可能的话,模拟电路和数字电路——包括各自的地和接地平面——应该分开。快速的上升沿会造成电流毛刺流入接地平面。这些快速的电流毛刺引起的噪声会破坏模拟性能。模拟地和数字地(以及电源)应该被连接到一个共用的接地点以便降低循环流动的数字和模拟接地电流和噪声。

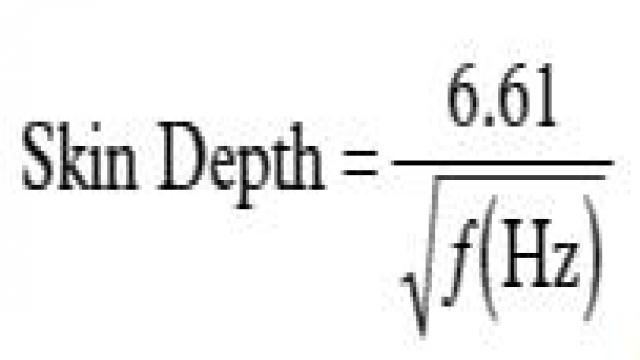

在高频段,必须考虑一种称为"趋肤效应"的现象。趋肤效应会引起电流流向导线的外表面——结果会使得导线的横截面变窄,因此使直流(DC)电阻增大。虽然趋肤效应超出了本文讨论的范围,这里还是给出铜线中趋肤深度(Skin Depth)的一个很好的近似公式(以cm为单位):

(5)

(5)

低灵敏度的电镀金属有助于减小趋肤效应。

封装

运算放大器通常采用不同的封装形式。所选的封装会影响放大器的高频性能。主要的影响包括寄生效应(前面提到的)和信号路径。这里我们集中讨论放大器的路径输入、输出和电源。

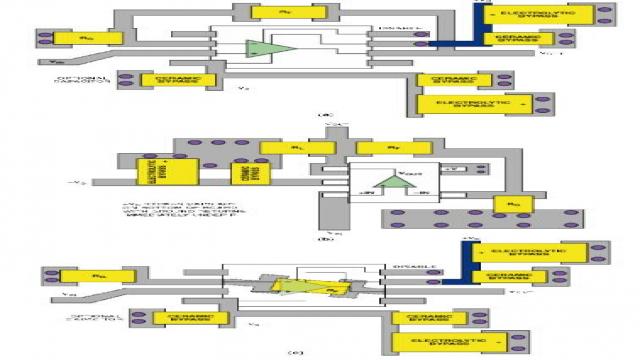

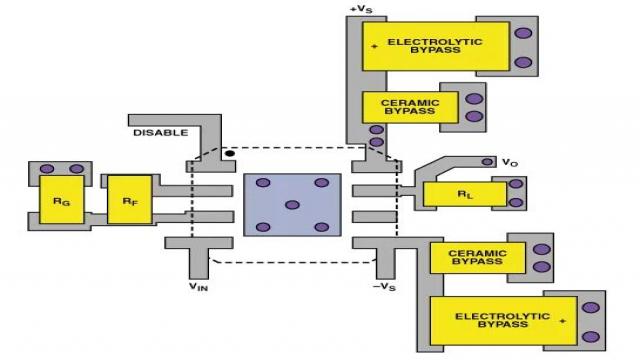

图9示出了采用SOIC封装(a)和SOT-23封装(b)的运算放大器之间的布线区别。每种封装都有它自身的一些问题。重点看(a),仔细观察反馈路径就发现有多种方法连接反馈。最重要的是保证印制线长度最短。反馈路径中的寄生电感会引起振铃和过冲。在图9(a)和9(b)中,环绕放大器连接反馈路径。图9(c)示出了另外一种方法——在SOIC封装下面连接反馈路径——这样就减小了反馈路径的长度。每种方法都有细微的差别。第一种方法会导致印制线过长,会增大串联电感。第二种方法采用了通孔,会引起寄生电容和寄生电感。在给PCB布线时必须要考虑这些寄生效应的影响及其隐含的问题。SOT-23布线差几乎是最理想的:反馈印制线长度最短,而且很少利用通孔;负载和旁路电容从很短的路径返回到相同的地线连接;正电源端的电容(图9(b)中未示出)直接放在在PCB的背面的负电源电容的下面。

图9. 同一运算放大器电路的布线区别。(a)SOIC封装,(b)SOT-23封装,(c)在PCB下面采用RF的SOIC封装。

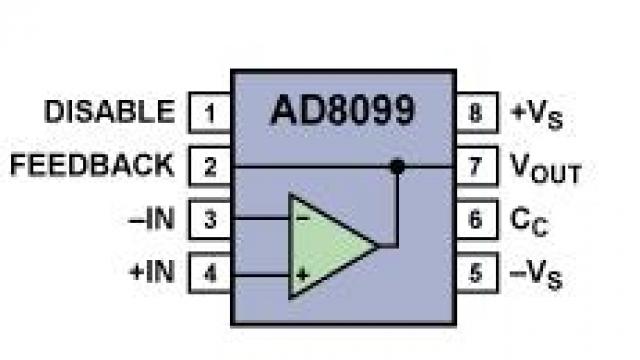

低失真放大器的引脚排列:ADI公司提供的一些运算放大器(例如AD80451)采用了一种新的低失真引脚排列,有助于消除上面提及的两个问题;而且它还提高了其它两个重要方面的性能。LFCSP的低失真引脚排列,如图10所示,将传统运算放大器的引脚排列按着逆时针方向移动一个引脚并且增加了一个输出引脚作为专用的反馈引脚。

图10. 采用低失真引脚排列的运算放大器。

低失真引脚排列允许输出引脚(专用反馈引脚)和反相输入引脚之间可以靠近连接,如图11所示。这样极大地简化和改善了布线。

图11. AD8045低失真运算放大器的PCB布线。

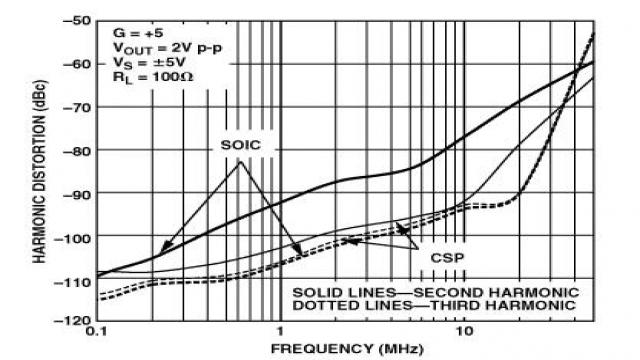

这种引脚排列还有一个好处就是降低了二次谐波失真。传统运算放大器的引脚配置中引起二次谐波失真的一个原因是同相输入和负电源引脚之间的耦合作用。LFCSP封装的低失真引脚排列消除了这种耦合所以极大地降低了二次谐波失真;在有些情况下最多可降低14 dB。图12示出了AD80992采用SOIC封装和LFCSP封装失真性能的差别。

这种封装还有一个好处——功耗低。LFCSP封装有一个裸露的焊盘,它降低了封装的热阻,从而能改善θJA值约40%。因为降低了热阻,所以降低了器件的工作温度,也就相当于提高可靠性。

图12 . AD8099不同封装失真性能对比——相同的运算放大器采用SOIC和LFCSP封装。

目前,ADI公司提供采用新的低失真引脚排列三种高速运算放大器:AD8045,AD8099和AD80003

布线和屏蔽

PCB上存在各种各样的模拟和数字信号,包括从高到低的电压或电流,从DC到GHz频率范围。保证这些信号不相互干扰是非常困难的。

回顾前面"谁都别信"部分的建议,最关键的是预先思考并且为了如何处理PCB上的信号制定出一个计划。重要的是注意哪些信号是敏感信号并且确定必须采取何种措施来保证信号的完整性。接地平面为电信号提供一个公共参考点,也可以用于屏蔽。如果需要进行信号隔离,首先应该在信号印制线之间留出物理距离。下面是一些值得借鉴的实践经验:

- 针对0.4毫米和0.5毫米晶圆级封装的PCB设计(07-28)

- 射频电路的PCB设计(12-04)

- 电子元件面对高功率电平(01-04)

- 射频板材选材和无源互调(01-05)

- AWR和Zuken发布PCB射频验证流程(01-30)

- 手机PCB可靠性的设计(04-23)