一种利用有源偏置控制器偏置射频/微波放大器的最佳解决方案

如果所需VNEG < −2.46 V,则R5 (kΩ) = 开路,且R6 (kΩ) = 50/(50 × (所需VNEG − 0.815)/(262 × (0.815 − 1.44)) − 1)。

如果所需VNEG > −2.46 V,则R5 (kΩ) = 262/(262 × (1.44 − 0.815)/(50 × (0.815 − 所需VNEG)) − 1),且R6 (kΩ) = 开路。

如果所需VGATE < −2.46 V,则R7 (kΩ) = 开路,且R8 (kΩ) = 50/(50 × (所需VGATE − 0.815)/(262 × (0.815 − 1.44)) − 1)。

如果所需VGATE > −2.46 V,则R7 (kΩ) = 262/(262 × (1.44 − 0.815)/(50 × (0.815 – 所需VGATE)) − 1),且R8 (kΩ) = 开路。

上电期间,如果VNEG达到默认值−2.46 V,则VNEG使能。因此,VNEG值必须小于VGATE值。

建议将HMC980LP4E的VNEG值配置为大于−3.5 V。

例如,若所需VNEG = −1.5 V且VGATE = −1.3 V,则R5 = 631 kΩ,R7 = 477 kΩ,R6 = R8 = 开路。此外,若所需VNEG = -3.2 V且VGATE = -3 V,则R6= 221 kΩ,R8= 303 kΩ,R5= R7 = 开路。

减少VGATE上升时间

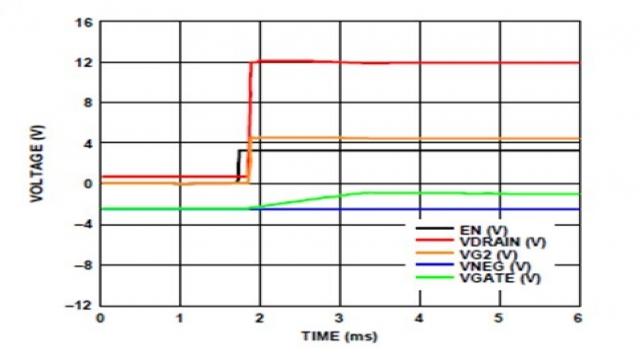

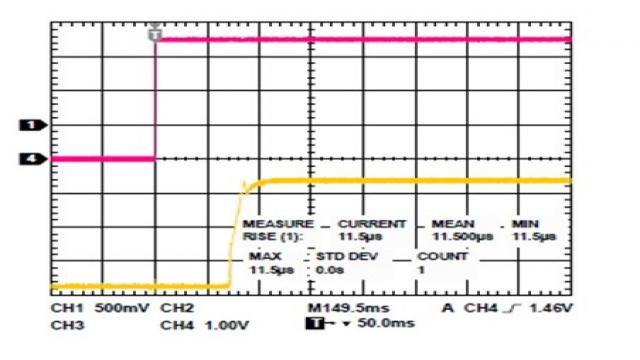

使能信号到达有源偏置控制器使能引脚的时刻,与DUT VGATE输入引脚的VGATE电压电平建立至所需值的时刻之间存在一个延迟。偏置控制器的内部传播延迟和VGATE信号的建立时间共同引起此延迟。有源偏置控制器VGATE输出与DUT VGATE输入引脚之间的连接上使用的分流电容会影响VGATE建立时间。HMC980LP4E典型使能波形(参见图16)表明VGATE建立时间大于1 ms。

图16.HMC980LP4E典型使能波形

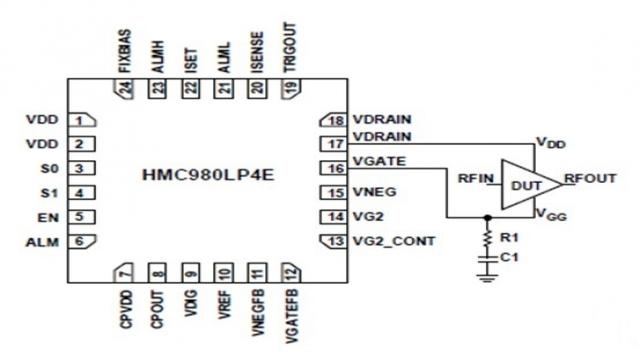

外部电路会影响栅极上升时间,但不影响传播延迟。图17显示了HMC980LP4E和DUT放大器之间的典型VGATE连接。分流电容C1一般用在放大器的VGG引脚上,R1通常为0 Ω,即不使用。

图17.HMC980LP4E和DUT之间的VGATE连接电路

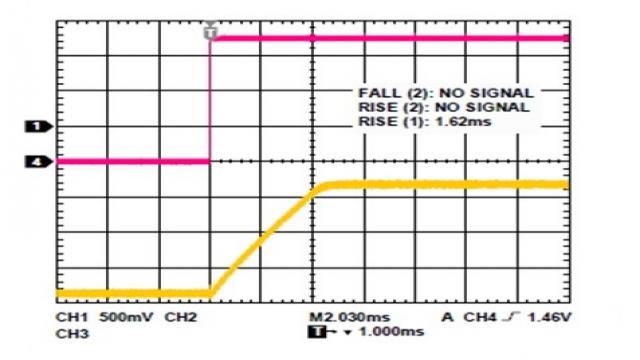

当C1 = 10 μF时,典型上升时间大于1.5 ms(参见图18)。C1减小到1 μF时,上升时间减少到131 μs(参见图19)。

图18.C1 = 10 μF时的典型VGATE上升时间

图19.C1 = 1 μF时的典型VGATE上升时间

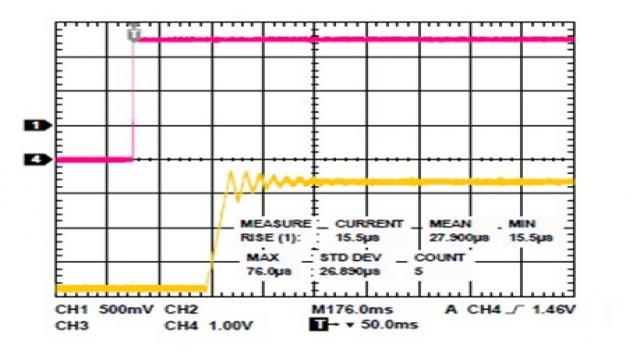

当C1 = 100 nF时,VGATE上升时间减少到15.5 μs,但过冲会引起响铃振荡(参见图20)。给C1 = 100 nF增加一个值为68 Ω的串联电阻R1,可以改善响应性能并使上升时间保持在类似水平(参见图21)。

图20.C1 = 100 nF时的典型VGATE上升时间

图21.C1 = 100 nF且R1 = 68 Ω时的典型VGATE上升时间

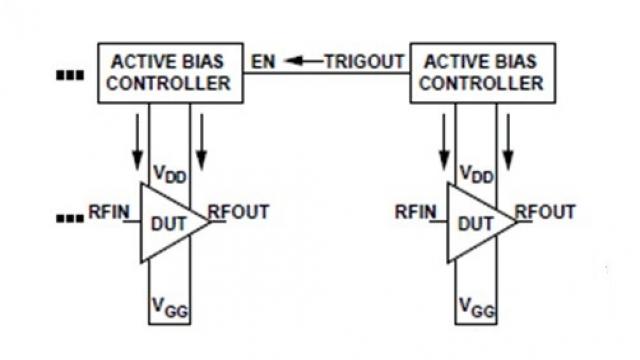

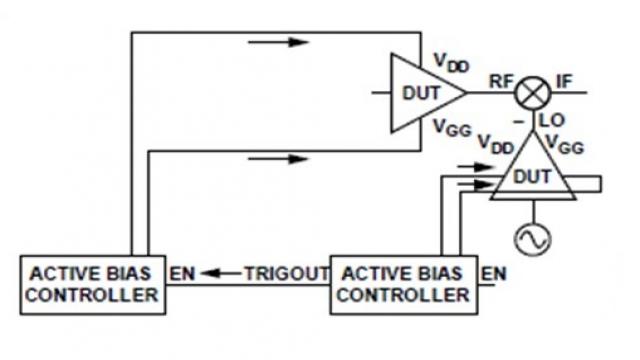

菊花链配置

当多个有源偏置控制器偏置多个DUT时,可以让其构成菊花链配置。当VDRAIN、VG2和VGATE输出建立时,有源偏置控制器产生TRIGOUT输出。利用TRIGOUT信号通过使能引脚(EN)使能另一个偏置控制器,可以提高系统安全水平。菊花链配置有很多应用,图22和图23显示了两种应用。DUT级数和偏置控制器数量可以增加。

图22.级联配置的两个放大器的菊花链配置

图23.DUT放大器位于不同信号路径上的菊花链配置

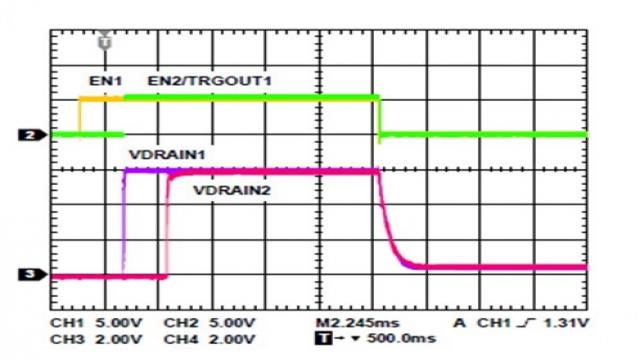

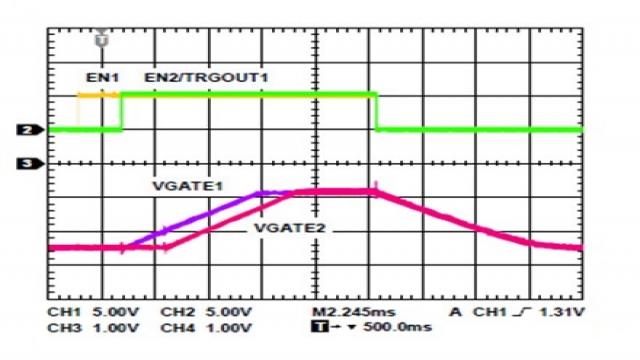

图24显示了菊花链配置中两个有源偏置控制器的VDRAINx和VGATEx响应,每个偏置控制器为一个DUT供电。第二偏置控制器由第一偏置控制器提供的触发信号使能。这种架构确保第二DUT在第一DUT使能后使能。

图24.菊花链配置中两个有源偏置控制器的VDRAINx响应,每个偏置控制器为一个DUT供电

图25.菊花链配置中两个有源偏置控制器的VGATEx响应,每个偏置控制器为一个DUT供电

测试有源偏置控制器的功能

有源偏置控制器的VDRAIN和VGATE输出可以偏置DUT,例如有外部偏置要求的FET或放大器。一旦将DUT连接到偏置控制器,反馈环路便闭合,偏置控制器即可工作。

对于带固定负载(如电阻)的有源偏置控制器,由于环路未闭合,因而无法测试其功能。

虽然测试无DUT的有源偏置控制器不会提供有用信息,但可执行如下诊断检查。

● IDD = 0 mA时,VDD输入和VDRAIN输出上的压降可忽略不计;因此,VDRAIN几乎等于VDD。 ● VNEG典型值为−2.46 V。 ● VGATE最大值为VNEG + 4.5 V,典型值为2.04 V。

对于其他偏置控制器,这些值可从数据手册中获得。

利用单个有源偏置控制器偏置多个DUT

可以利用单个有源偏置控制器来偏置两个或更多DUT。为此,计算RSENSE值时应考虑DUT的总漏极电流。

但应注意,使用这种方法会限制有源偏置控制器的优势,原因如

- 如何选择合适的射频电感(04-22)

- 亚运在深圳系列之四:曾经的挂科王(11-21)

- 射频电路的PCB设计(12-04)

- Wi-Fi产品射频电路EVM降低的一般原因(03-01)

- 手机射频电路组成和特点分析(07-13)

- RFIC的沧海桑田(08-01)