基于PC/104总线的多功能扩展通讯模块的设计

·CAN控制器SJA1000的对外操纵接口是一种地址/数据分时复用的接口,而PC104没有地址/数据分时输出的特性。因此,必须经过期序转换才能实现它们之间的连接。目前,一般采用8031单片机转发数据的方式来实现:通过8031连接CAN控制器,104PC利用IO端口读写的方式将数据直接传送给8031,或者将数据写于双口RAM中,8031在另一个口读取数据,再由它对CAN总线控制器进行操纵,将数据转发出往。这种方法无疑又要增加器件和电路的复杂性。

为此,设计了通过CPLD整合时序实现104PC与CAN控制器连接的方法,由104PC分时送出操纵地址和操纵数据,并由CPLD整合相关的逻辑控制信号,满足CAN控制器的时序要求。

·采用CPLD可以根据需要定义输进输出脚,方便PCB板布局和走线。

·采用CPLD时不必担心设计中所采用器件的种类、数目,可以任意定义所需各种器件,从而优化电路性能。

·采用CPLD可以通过软件对电路进行仿真,方便电路调试。

·采用CPLD可以在线修改其内部逻辑,升级或修改BUG时可不改动外部电路。

CPLD芯片选用ALTERA公司的EPM7064SLC84-10,该芯片具有基于EEPROM的第二代MAX结构,支持通过JTAG引脚实现在系统编程。拥有64个宏单元,4个逻辑阵列块,1250个可用门单元,支持5V/3.3V多电压IO接口,可提供68个用户IO引脚。

根据以上的方案,通讯扩展模块的结构如图1。

图1 扩展通讯模块结构

3 硬件实现

3.1地址译码电路

本扩展模块共需占用七个IO地址,其中两个IO地址供CAN控制器,四个IO地址供四串口异步通讯单元,一个IO地址供中断共享电路。必须公道选择IO地址,否则会引起系统不可预知的冲突。

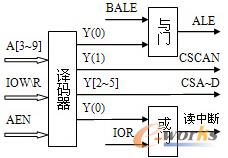

各种PC104计算机IO地址分配情况大体相同,以盛博SysCenterMoudle/SuperDx为例,选择了110H~140H为扩展通讯模块的IO地址,地址分配见表1,逻辑译码结构见图2。

表1 IO地址分配表

图2 IO地址逻辑译码结构

图2用VHDL语言可以很方便地实现。其具体描述如下:

SEL(0)<=AEN;

SEL(1)<=NIOW AND NIOR;

SEL(2)<=ADDR(0);

SEL(3)<=ADDR(1);

SEL(4)<=ADDR(2);

SEL(5)<=ADDR(3);

SEL(6)<=ADDR(4);

SEL(7)<=ADDR(5);

SEL(8)<=ADDR(6);

WITH SEL SELECT

Y<="1111110" WHEN "010001000",//IO/110 地址操纵

"1111101" WHEN "010001100",//IO/118 数据操纵

"1111011" WHEN "010010000",//IO/120 串口1

"1110111" WHEN "010010100",//IO/128 串口2

"1101111" WHEN "010011000",//IO/130 串口3

"1011111" WHEN "010011100",//IO/138 串口4

"0111111" WHEN "010100000",//IO/140 读中断号

"1111111" WHEN OTHERS;

END BLOCK CODE;

3.2 104总线与CAN控制器的接口

如前所述,104总线与ISA总线兼容而与CAN控制器要求的时序不同,设计中将104总线中的BALE、地址和读写信号经CPLD逻辑整合后提供给CAN控制器,同时从数据线分时送出操纵地址和操纵数,满足CAN控制器的时序要求。时序整合的VHDL语言如下:

ALE<=(NOT Y(0)) AND BALE;

CSCAN<=Y(1);

IORCAN<=Y(1) OR NIOR;

IOWCAN<=Y(1) OR NIOW;

双向数据缓冲的VHDL实现可以在很多参考书中找到,此处从略。

3.3 异步通讯接口电路及中断共享电路

16554的接口可与PC104实现无缝连接,CPLD实现选通和读写逻辑控制,异步通讯与CAN控制器共用CPLD内的双向数据缓冲电路。

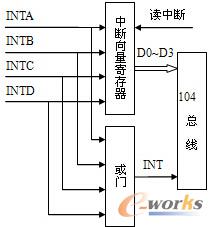

异步通讯控制单元16554有很强的中断能力,四个串行控制用具有各自的中断引脚,使用灵活。但系统的中断资源有限,假如每一个控制器都占用一个中断号,通讯模块需要占用五个中断号。为了节约中断资源,设计中将4个串口控制器共享一个中断,而CAN总线控制器单独占用一个中断。

为了实现共享,设置了一个中断向量寄存器,当发生中断时首先读取中断向量寄存器以定位发出中断的串行口。其原理见图3。

图3 中断共享电路

VHDL语言实现如下:

GMID<=NIOR OR Y(6);

INTSER<=INTABCD(0) OR INTABCD(1) OR INTABCD(2) OR INTABCD(3);

INTID<=INTABCD WHEN (GMID=‘0‘)

ELSE

"ZZZZ"

4 结论

本设计利用CPLD实现了104总线和CAN控制器之间的时序转换、整个电路的逻辑控制以及中断共享,使电路设计结构紧凑,性能稳定。扩展了RS-232、RS-485和CAN接口的104PC可以满足尽大部分控制系统的通讯要求。该设计已被一个分布式防空系统所采用,在历次联调试验中性能指标均达到了要求。

总线通讯模块控制 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)