基于1394总线通信的I/O模块在数控系统中的应用

数控系统作为数控机床装备的核心关键部件,是决定机床装备的性能、功能、可靠性和成本的关键因素。我国的数控系统技术基础薄弱,高档数控系统基本依赖进口,而相关高档数控系统的开发技术,国外对我国至今仍封锁限制,成为制约我国高档数控机床发展的瓶颈。自主开发高档数控系统迫在眉睫,而其中的关键技术就是数据通信速率的提高。

IEEE 1394最初由Apple公司提出,命名为FireWire(火线),是一种高速串行总线。IEEE(电气和电子工程师协会)在1995年认可FireWire为IEEE1394—1995规范,继而又对该协议中一些模糊的定义加以修正,推出了IEEE 1394a.2000规范,解决了一些兼容性问题。2001年,更新的1394规范——1394b也被推出,其带宽、传输速度、距离和效率都有了大幅度提高。IEEE 1394支持100 Mb/s、200 Mh/s和400 Mb/s的传输速率;支持点到点的传输,各个节点可以脱离主机自主执行事务;另外,它还支持即插即用、热插拔、同步和异步传输方式,公平仲裁原则。鉴于IEEE 1394的高速传输等优越性,将其应用于高档数控系统成为一种必然的趋势。

本研究设计出一块基于1394总线传输的I/O模块,该模块应用在高档数控系统中,负责实时采集机床开关量数据,数据传输及控制机床进给量。

1 1394总线通信I/O模块硬件设计

1.1 I/O模块整体结构介绍

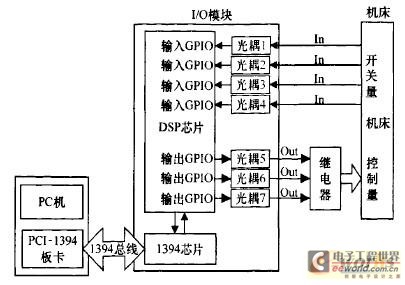

该模块主要包括1394芯片、DSP芯片和光耦芯片。该模块共引出32个输入口和24个输出口,具有高速传输、抗干扰的特点。该模块I/O端El通过排线与数控机床的开关量相连接,负责数据采集及实时控制。1394端口通过1394总线与上位机进行通信,负责I/O模块与上位机的数据传输。该模块与上位机及机床的整体架构如图1所示。

图1系统整体结构图

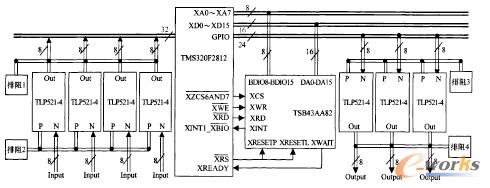

I/O模块中各芯片间的连接如图2所示:DSP芯片选用TI公司的TMS320F2812,它是一款32位定点DSP芯片,运行速度高,处理功能强大,并且具有丰富的片内外围设备,便于接口和模块化设计。共有56位复用GPIO,可引出作为I/O端口。1394芯片选用TI公司的TSB43AA82,它是一款集成物理层和数据链路层的两端口1394控制器,兼容1394—1995和IEEEl394a一2000规范,支持异步数据传输。光耦芯片选用TOSHIBA公司的TLP521-4,每个芯片内具有4个独立隔离通道旧J。DSP芯片与1394芯片通过数据线、地址线和控制线连接。DSP芯片引出56位GPIO管脚,通过光耦芯片与外界设备连接。

图2 I/O模块中1394,DSP及光耦芯片的连接

1.2 DSP芯片外围电路介绍

TMS320F28 12的XZCS6 AND7连接TSB43 AA82的xcs(片使能),用于片选TSB43AA82,当访问区域6时有效;XWE为写有效,连接TSB43AA82的XWR(写使能),用于向TSB43AA82写入数据;XRD为读有效,连接TSB43AA82的XRD(读使能),用于读取TSB43AA82数据;XRS为复位输出,连接ARESETP(物理层模块复位输入)和ARESETL(链路层模块复位输入),用于控制TSB43AA82复位;TSB43AA82的XINT为中断信号输出,连接TMS320F2812的XINTl一XBIO中断输入),用于中断程序;XWAIT为等待信号输出,连接TMS320F2812的XREADY(数据准备输入),用于说明外设已为访问做好准备;XA0~XA7,BD108~BDI015为8位地址总线,XD0~XDl5,DA0~DAl5为16位数据总线,用于TMS320F2812与TSIM3AA82之间数据传输。TLP521-4的P为内部发光二极管正极,N为内部发光二极管负极,Out为内部三极管输出。

1.3 光耦芯片电路介绍

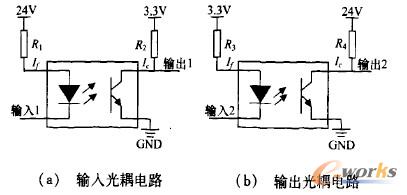

本设计的I/O模块通过引入光耦芯片,实现DSP芯片与机床的电路隔离、电平匹配等功能。光耦芯片电路如图3所示。输入光耦电路指I/O模块输入端,“输入1”连接机床开关量;“输出1”连接DSP的输入GPIO。输出光耦电路指IZO模块输出端,“输入2”连接DSP的输出GPIO;“输出2”通过继电器连接机床的控制量。

图3光耦电路图

根据光耦芯片TLP521-4的使用条件,Ic范围应在0~10 mA;,If范围应在0~25 mA;Ic/If范围应在100%~600%。又根据光耦芯片内部结构可知,输入部分为一个发光二极管,故其工作电流,,不可太小。对于输入光耦电路,选取R1=4.7kΩ,R2=470Ω,则有Ic=7.02 mA,If=5.11 mA,Ic/If=137Ω;对于输出光耦电路,选取R3=1kΩ,R4=4.7kΩ,则有Ic=5.11 mA,If=3.3 mA,Ic/If=155%,均在正常工作范围内。

2 I/O模块通信软件设计

IEEE 1394协议支持异步传输和等时传输两种机制。本设计采用的是异步传输模式,其特点是叮靠,通过发送ACK信号及响应包来实现。1394芯片为收发数据准备了FIFO空间。针对异步传输的是ARF(异步数据包接收FIFO),ATF(异步数据包传输FIFO)空间,空间大小可以进行配置分配,FIFO空间总和为512个Quadl

1394总线通信IO模块数控系 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)