一“芯”二用,MCU+DSP处理器大盘点

集和总线结构,扩展的并行性,片上编程和数据内存,先进的调试和测试功能使得内核能很好地解决实时性问题、嵌入式DSC 和控制任务。

内核编程模式

DSP56800E 的内核寄存器被认为是内核编程模式的一部分。如图2-1 所示。片上模块的寄存器被映射到数据存储器的64 个单元上,注意,这64 个单元在特定的设备上可以位于数据存储器的任何位置。使用内存块的实例如表2-1 所示。可以参考特定器件的用户手册得到其模块的细节描述,包括它们的功能,存储区的寄存器及其映射到内存的位置。

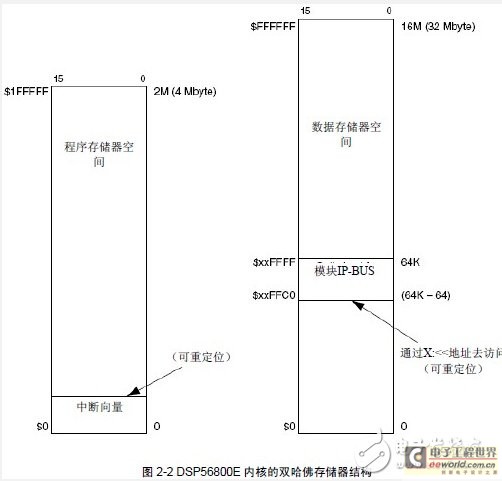

双哈佛存储器

DSP56800E 具有程序存储区与数据存储区分开的双哈佛结构,如图2-2 所示。这种结构允许同时进行对程序存储区和数据存储区的读写操作,而且数据存储器支持同时2个地址的读操作,支持最多达3个地址单元的存储器操作。

在程序存储器中,包含了可以任意大小和放在任意位置的复位中断向量。外设寄存器被映射到数据存储器的64个字的地址单元。

外设寄存器的64个字的地址单元原则上可以被重映射到任意地址。为了不重叠RAM 和ROM 数据存储块,64 个字单元的地址通常被特别设定,X:《《pp 寻址模式提供了针对64 个单元的高效访问,提供了单字,单周期转移和位操作指令。

注意在64 个单元的最上面12 个单元被DSP56800E 内核保留使用,用于中断优先级,总线控制寄存器。

DSC实例

DSC 是一种能对周期性地采样和数字化的实时信号进行算术的处理器,DSC 实例都包含以下几个方面:

滤波

卷积(混合两个信号)

相关(比较两个信号)

整流,放大和传输

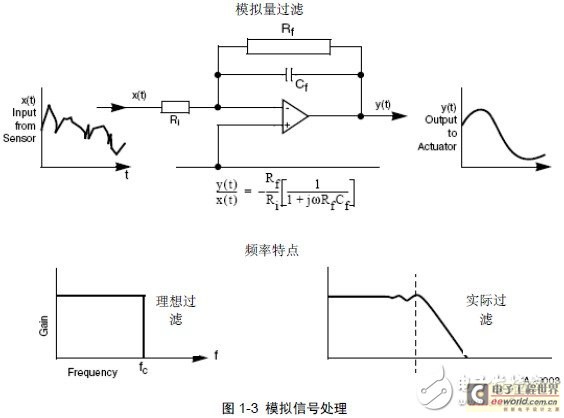

图1-3 是1 个模拟信号处理的例子。图中的电路过滤了来自的传感器的信号,传感器信号采集电路使用了1 个可调节的放大器,并利用该结果控制1 个动力臂。理想的滤波器是无法设计出来的,工程师设计滤波器时必须尽量满足:可接受的响应性,不同温度的变化,元器件老化,电源波动和元器件的精度等因素。按照这样要求设计出来的电路一般具有很低的抗干扰性,需要经常调整参数且难于修改。

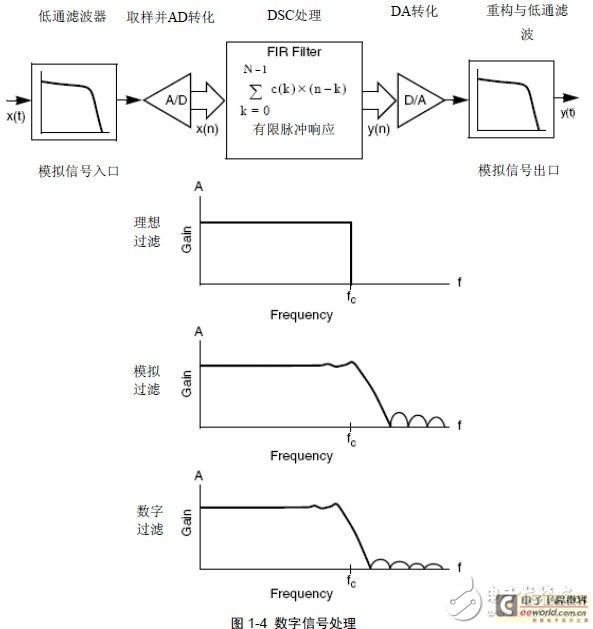

使用 DSC 的等效电路如图1-4 所示。这个应用除了DSC 之外,还要求1 个A/D 转化器和D/A 转化器。

上图的处理电路首先通过 1 个滤波器限制输入信号的波段,将去除了超过波段的干扰信号。然后信号被取样,通过AD 转换器数字化并送入DSC 进行数字化处理。DSC的输出通过DA 转化成模拟信号并通过低通过滤,消除数字化的影响。

通过DSC 执行的特定的滤波严格来说是个软件的过程。DSC 能执行任何使用模拟技术实现的滤波器。而且,使用模拟技术很难实现的自适应性过滤,能很容易的通过DSC 实现。

总之,使用DSC 的优势如下:

更少的元件

稳定,确定的性能

无需调整滤波系数

广泛的应用范围

更加鲜明的过滤特点

抗噪声能力强

易实现自适应性过滤

具有自测试功能

较好的电源干扰抵制机制

DSP56800E 系列不是为了一个特定的应用专门定制的IC 芯片,而是作为一种通用目的的DSC 结构,用于高效的执行普通DSC 算法和控制代码。

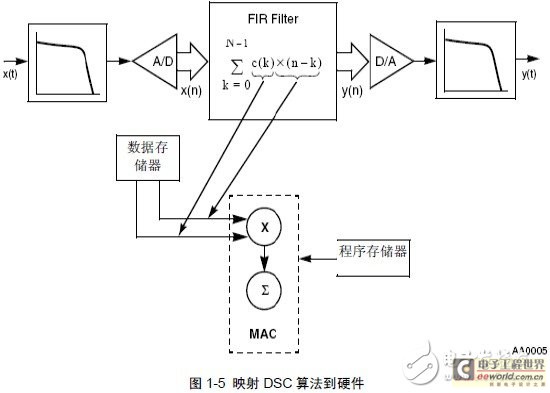

如图1-5 所示,DSC 关键的属性如下:

乘法累加(MAC)操作

MAC 的每个指令周期取2 条操作数

强大的指令集保证了执行的灵活性

移入/出DSC 数据

MAC 操作是一个在DSC 中的基本操作,DSC56800E 双哈佛结构优化了MAC 操作,通过同时对两个独立的数据单元存取使得乘法操作和加法操作在一个MAC 时钟周期内完成。整个过程必须在程序的控制下才能完成从乘法器的取数和对计算结果的转存。由于内存和MAC 是互相独立的,DSC 能在一条指令内执行两个内存的数据交换,一个乘法和加法运算,两个地址的更新等操作,使得很多DSC 级的处理器能更加高效的执行乘法运算。

MCU+DS 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)