采用CMRC结构的Ka波段四次谐波混频器设计

时间:12-21

来源:互联网

点击:

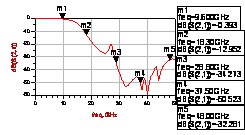

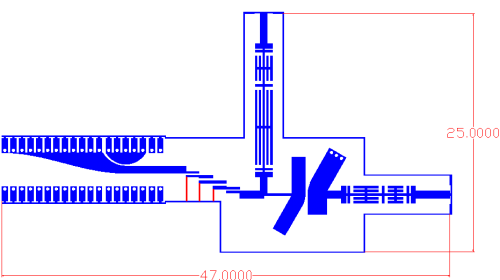

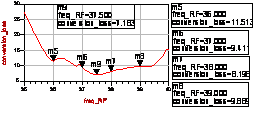

37.5GHz更多抑制了20dB左右。而且高低阻抗线设计的滤波器在0~50GHz范围内约有3、4个寄生通带,影响了整个系统的带宽,而本设计完全消除了这些寄生通带。 在本振输入端,应该通本振(9.6GHz),阻射频(37.5GHz)、本振奇次谐波(3LO=28.8GHz、5LO=48GHz)、射频与偶次本振的谐波(RF-2LO=18.3GHz)。 同中频低通滤波器设计类似,也采用两个CMRC级联形式,其中一级长度也选2.6mm,二级长度选1.6mm,级联后HFSS仿真结果如下: 图8 本振端滤波器仿真结果 它对20GHz以后的频率都有了20dB以上的抑制,很好满足了设计的要求。 5 整体电路设计 最后,经过优化设计的整体电路如图9。电路左侧为射频输入,右侧为本振输入,中频由上端输出。 图9 整体电路加工图 结合HFSS和ADS,仿真得变频损耗随射频输入频率变化结果如图10: 图10 Ka波段四次谐波混频器变频损耗 由图可见,15dB以下变频损耗带宽约有4.5GHz,最低变频损耗为7.2dB。 6 总结 本文介绍了谐波混频器的基本原理,分析了CMRC结构的慢波、宽带阻特性,据此设计出一种性能良好的Ka波段宽频带四次谐波混频器。变频损耗在15dB以内的带宽有4.5GHz。在射频频率37.5GHz,本振功率10dBm,中频频率900MHz时,变频损耗为7.2dB。实验研究工作正在进行中。 4.3 本振滤波器设计

ka波段CMRC谐波混频器低变频损 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)