基于FPGA的AFDX终端系统模块设计

1 引言

本文在研究航空全双工交换式以太网(Avionics Full Duplex Switched Ethernet,AFDX)实时传输协议的基础上,分析了基于CPCI接口的双冗余AFDX终端测试系统通讯模块的设计原理,重点介绍了支持热插拔的CPCI接口电源电路分析、FPGA与PCI9030接口模块时序分析和在Windriver软件环境下的驱动程序的开发,为AFDX上位机底层驱动接口的开发和软件界面的开发以及AFDX交换机的研发打下了良好的基础。

2 AFDX终端系统模块设计

本文设计的AFDX终端通讯系统包括FPGA控制模块、PCI接口模块、双冗余PHY模块。为了设计高可靠性的AFDX终端系统,设计了2个独立的双冗余交换网络,从而保证系统的可靠性信息传输。系统硬件架构如图1所示。

2.1 CPCI接口模块

CPCI接口模块由2个部分组成,第一部分主要实现PCI总线协议功能,实现FPGA与上位机进行数据的通信;第二部分主要实现从CPCI接口采电,并在板上进行电源管理,对整个板卡实现支持热插拔的电源供应。

2.2 FPGA控制模块

FPGA控制模块是整个板卡的控制核心,它包含了AFDX协议栈的IP硬核,实现了AFDX协议栈特有的,如流量整形、虚拟链路调度、完整性检查、冗余管理、以太网MAC层硬件实现等功能以及其它如与PCI9056通信、内部数据的缓存管理等功能。支持10/100Mbps标准的航空实时以太网数据的可靠性传输。

以数据下传为例介绍FPGA控制模块的工作流程:首先在PC机上运行上层测试软件,通过它来设置发送通道的相应参数,该信息通过CPCI接口传送至可编程芯片,可编程芯片内的处理器单元根据PC机下传的参数来设置发送通道的相关寄存器参数,同时该消息经过流量整形模块,进行规划化处理,使其输出的数据帧是规整的、没有时延抖动的。来自流量整形模块的数据帧由虚拟调度模块添加序列号(SN)后,发往冗余管理模块。冗余管理模块将需要发送消息复制发送到2个独立的冗余MAC链路层中。 MAC模块对数据帧添加帧序列校验,发往PHY模块。PHY层模块将可编程芯片内的MAC层的数据帧进行电平转换后传送至其他标准航空以太网PHY设备中。

2.3 双冗余PHY物理接口

双冗余的PHY模块实现以太网物理层的接口功能,实现AFDX航空以太网的可靠性传输,FPGA内部的航空以太网MAC层通过MII接口与PHY连接,完成数据流的通信。MII (Media Independent Interface 介质无关接口) 接口,即媒体独立接口,它是IEEE-802.3定义的以太网行业标准。它包括一个数据接口,以及一个MAC和PHY之间的管理接口。数据接口包括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。MII数据接口总共需要16个信号。管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY.本设计中采用的是双PHY芯片共用一个25MHz的外部晶振提供工作时钟,这样可以保证双冗余的PHY完全工作同步。

3 CPCI接口电源电路分析

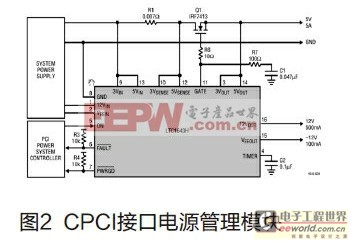

热插拔功能主要用于CPCI设备,热插拔功能允许板卡随意从设备中插拔而不影响设备操作系统的正常运行。如图2所示,LTC1643L是一个允许CPCI型设备进行安全插入和拔出的电源管理控制器,将系统的CPCI插槽电源接入到AFDX板卡,图中IRF7413是一个N型MOS管,用于控制3.3V和5V的电源供应,而-12V和+12V电源由片上开关供应,所有的电压的上升时间可以达到一个可编程的速率,同时还有电源过流故障时的短路保护。

PCI9030的引脚BD_SEL#是CPCI接口中最小的插针之一,BD_SEL#连接LTC1643L的使能引脚,低电平时有效开启LTC1643L工作并同时给板卡供电。R10是一个0.018欧姆,0.5W,精度为1%的精密电阻,用于过流保护的电压检测电阻。当板卡发生故障导致电流超过额定值之后,R10两端的压差将增大,SENSE引脚将此过流信息反馈至LTC1643L电源管理器,同时切断电源供应,起到电源过流保护的功能。

4 FPGA与PCI9030接口模块时序分析

在PCI9030与本地FPGA之间的通信分为直接主模式(Direct Master Mode)、直接从模式(Direct Slave Mode)和DMA模式。由于PCI通信要AFDX网络的10M/100M通讯速率,这里采用直接从模式,工作时序如图3所示,PCI9030为主,FPGA为从。LHOLD为输出,声明使用本地地址数据总线,LHOLDA为本地总线申请使用成功的返回信号。LBE[3:0]#为本地总线使能控制引脚,这里选择32位宽的数据总线。LA[31:2]为地址总线,在本地总线申请使用成功信号返回且本地总线位宽使能有效后,开始输出地址信号。ADS#为起始信号,表明地址总线有效且开始一个有效的总线访问,同时一个周期后就可以读数据或者写数据了,LW/R#低电平为读高电平为写。

FPGAAFDXPCI总 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)