基于CAN总线的飞行模拟器通信接口设计

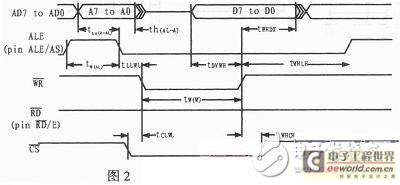

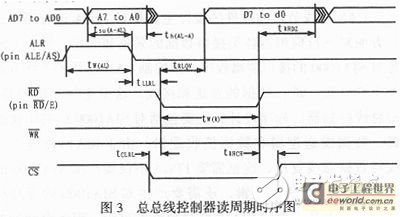

软件系统设计 CAN总线节点的软件的设计主要是对FPGA进行编程,一方面对飞行模拟器各类接口数据的采集和输出,另一方面是对SJA1000的接口逻辑程序,来控制CAN总线的工作方式和工作状态,进行数据的发送和接收。这里主要介绍FPGA对总线控制器的程序设计,主要包括对SJA1000的初始化逻辑、数据发送逻辑和数据接收逻辑。由于SJA1000地址总线与数据总线复用,这就需要FPGA不仅要产生SJA1000读写控制引脚的信号逻辑,还需要产生对SJA1000的寻址信号,实际上是一个向SJA1000写地址的过程。因此设计的关键就是把SJA1000中的寄存器地址当成数据写入到SJA1000中,同时配合地址锁存信号ALE和写允许信号WR完成对SJA1000特定寄存器的命令字写入。 2.1 SJA1000初始化逻辑 初始化逻辑的主要功能是在系统上电或重启后,对SJA1000进行初始化,以确定工作主频、波特率、输出特性等。SJA1000支持两种模式,即BasicCAN模式和PeliCAN模式,BasicCAN模式是上电后默认的操作模式。SJA1000的初始化逻辑主要包括工作方式的设置、验收滤波方式的设置、验收屏蔽寄存器(AMR)和验收代码寄存器(ACH)的设置、中断允许寄存器(IER)的设置、总线定时寄存器(BTR0、BTR1)、输出控制寄存器(OCR)和时钟分频器(CDR)的设置等。在完成SJA1000的初始化设置以后,SJA1000就可以回到工作状态,进行正常的通信任务。 2.2 数据发送逻辑 数据发送逻辑需要FPGA通过模拟总线的方法对SJA1000进行控制,SJA1000的发送缓冲区的寄存器共有11个字节,其中前3个字节分别是帧信息字节和两个标识码,后8个字节是数据。发送时,用户需要将待发送的数据按特定的格式组合成一帧报文,送入SJA1000的发送缓冲区中,然后启动SJA1000发送即可。需要注意的是,在向SJA1000发送缓存区送报文之前,必须先判断发送缓冲区是否锁定,如果锁定则等待;判断上次发送是否完成,如未完成则需等待发送完成。总线控制器写周期的时序图如图2所示。 2.3 数据接收逻辑 与数据发送逻辑类似,从接收缓冲区中读取一条报文也需要连续读取11个字节,数据接收逻辑除了正常的报文数据接收,还要实现其他情况的处理。对接收缓冲区的数据读取完毕后要释放CAN接收缓冲区。图3所示为总线控制器读周期的时序图。 在FPGA程序编写时,采用状态机完成逻辑的设计,分别包括初始化状态、空闲状态、查询状态、数据接收状态、数据发送状态。 3 结论 在系统设计过程中,采用ALTERA公司的EP1C6型FPGA进行设计,在Quartus II环境中利用Verilog HDL编程产生SJA1000的片选信号、地址锁存信号以及读写信号等,这些信号共同驱动SJA1000完成数据的发送和接收。在采用FPGA实现对SJA1000的逻辑控制过程中,采用Quartus II中的SignalTap II Logic Analyzer工具对FPGA各接口信号进行了测量,经检查各种逻辑均符合SJA1000的接口时序要求。 基于FPGA的飞行模拟器通信接口设计主要由Verilog语言进行描述,易于修改和移植,同时由于FPGA的I/O丰富,还可以将模拟器中一些常用的开关量连接到FPGA上,这样就可以将多种功能集成在一个FPGA上,相较于采用单片机控制SJA1000实现CAN总线通信,本设计方案可扩展性好,稳定性高,能降低成本、系统体积及功耗,在飞行模拟器领域中具有广泛的应用前景。

EP1C6飞行模拟器CAN总 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)