FPGA中定时循环启动开销测试

1. 背景及目的

在FPGA代码中,会遇到将定时循环嵌入非定时循环的情况,此时定时循环将反复启动和停止。这个定时循环的时间开销如何,需要测试验证。

定时循环的时间开销应包含两个方面:1.定时循环的启动开销,2.定时循环的运行开销。

对于第1点,目前没有找到FPGA的具体说明信息,而且这个时间开销应该和具体的时钟配置相关。

对于第2点,FPGA编译保障了每遍运行时间严格按照指定时钟周期运行。

所以,可以编写简单程序测试FPGA定时循环的启动时间开销。

2. 测试方法

软硬件环境:LabVIEW 2011,LabVIEW FPGA 2011

NI PXI-7851

测试配置及代码:

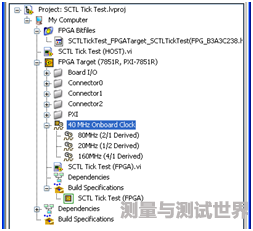

1.FPGA Target下新建多个时钟

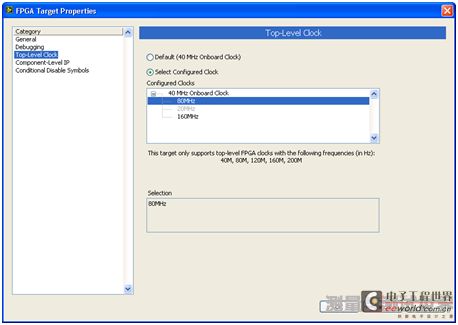

2.FPGA Target的top-level clock配置为80MHz时钟

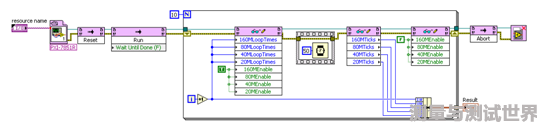

3.FPGA代码中对不同时钟运行指定次数进行计时

4.Host端指定循环次数,并读取每次的计时结果

3. 测试结果

由于Top-Level clock是80MHz,所以所有计时器的1个Tick代表的是80MHz时钟的1周期,

在160M时钟下,定时循环的启动时间开销约10个Tick,运行时间是每遍循环0.5个Tick;

在80M时钟下,定时循环的启动时间开销约1个Tick,运行时间是每遍循环1个Tick;

在40M时钟下,定时循环的启动时间开销约为28个Tick,运行时间是每遍循环2个Tick;

在20M时钟下,定时循环的启动时间开销约为48个Tick,运行时间是每遍循环4个Tick。

结果表明:

与Top-Level Clock 相同时钟驱动的定时循环的启动时间开销大大小于其他时钟下的定时循环。

在非Top-Level Clock情况下,定时循环的时钟频率越低,启动时间越长。

4. 结论

在FPGA代码中,

尽量避免循环的嵌套。尽量让最外层循环为定时循环。

定时循环的启动有时间开销。如果在非定时循环中反复运行定时循环,需要考虑定时循环的启动开销。

尽量让非定时循环中的定时循环工作在Top-Level Clock下,此时的启动开销为1个Tick。

FPGA定时循环启动开销测 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)