FPGA的并行多通道激励信号产生拈

引 言

并行测试的实现途径分为软件方式和硬件方式。用软件方式实现并行测试,关键是对测试任务的分解和调度,但可能会产生竞争或者死锁现象。因此,在测试资源有限并且任务分解和调度算法不成熟的情况下,用软件实现并行测试会很困难。用硬件方式实现并行测试时,需要通过提供充足的测试资源来满足并行测试的需求,而并行测试过程中激励资源不足同样会造成任务分解和调度难度增加,甚至导致竞争和死锁,影响并行测试实现。因此,对多通道并行激励信号的需求也是影响并行测试的关键因素。

1 并行测试技术

并行测试技术是把并行技术引入测试领域中,可以较好地完成同时对多个被测对象(UUT)任务进行测试的一种先进的测试方法和技术,属于下一代测试技术范畴,是支撑NxTest ATS的新技术之一。它根植于并行处理技术,其宏观表现为:在并行测试程序的控制下对多个被测对象(UUTs)同时测试。相比传统顺序测试技术,它通过对系统资源的优化利用,可以大幅度提高测试效能及测试质量,提高测试资源利用率,降低整个武器装备测试成本。因此,研究并行测试技术对我国测试技术的发展和提高武器装备战时的快速维护保障能力具有重要意义。

2 多通道波形产生模块

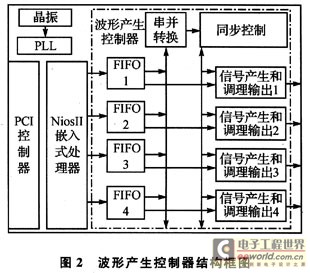

设计采用Altera公司的EP2C35作为整个系统的控制芯片,承担整个并行多通道信号产生模块的控制工作,内部主要包括Nios II嵌入式软核、波形产生控制器、PCI控制器等。

多通道波形产生模块主要包括4个子模块,分别为波形产生控制模块、信号产生模块、同步电路模块和调理输出模块。波形产生模块采用DDS技术,该技术产生的波形具备波形频谱纯净,稳定度高,切换时间短,频率、相位和幅度可调等特点。设计中采用ADI公司的AD9854芯片来实现此模块的功能。

波形产生模块为4个通道,各通道之间相互独立,且可以在不影响其他通道工作的情况下独立地发起或者终止输出。同时为了满足测试系统对多路同步激励的需求,模块还需具备多通道同步的能力,并可以配置同步的通道数量及各通道间相互信号关系。输出激励的控制命令信号经PCI总线传输到FPGA中,FPGA将接收到的命令经过解析后分别送入同步模块、DDS信号产生模块和调理输出模块。各通道的DDS信号产生模块接收到控制命令后与同步模块配合产生同步或者异步激励,最后由调理输出模块实现输出波形的滤波和幅度控制。图1为多通道波形产生模块硬件设计原理框图。

3 多通道波形控制器

3.1 结 构

波形产生控制器是整个模块正常运行的核心,主要完成信号产生控制、信号增益控制以及同步控制。多通道波形产生控制器主要由异步FIFO、同步逻辑与信号产生和调理输出组成,图2为波形产生控制器的结构框图。用户控制命令经PCI控制器传输至Nios II嵌入式软核后,首先经过译码处理,将控制命令按通道进行分类,而后传输至波形产生控制器中的异步FIFO进行缓冲。此刻各通道的控制命令主要包括同步命令、信号产生控制字以及增益控制命令,经过串/并转换后的同步命令控制着通道间的同步时序关系,而信号产生控制字和增益控制字则以并行方式输出至外围电路中,完成信号产生和调理输出。

3.2 实 现

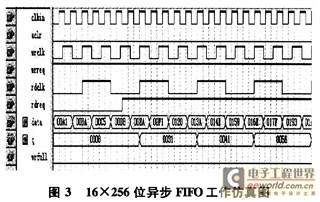

3.2.1 异步FIFO

多通道信号产生控制器中具有4个独立的FIFO,主要用于缓冲PCI控制器与波形产生控制器2个异步时钟域的数据传输,主要包括读/写时钟信号、读/写请求信号、数据输入/输出信号和空/满标志位。读请求信号(rdreq)有效时,在读时钟(rdclk)的上升沿处FIFO输出数据;写请求信号(wrreq)有效时,在写时钟(wrclk)的上升沿处FIFO写入信号;空/满标志位决定了数据能够写入或读出,模块中采用写满标志位(wrfull)来表示FIFO内部存储空间的使用情况。图3为16×256位的异步FIFO工作仿真图。

3.2.2 同步逻辑

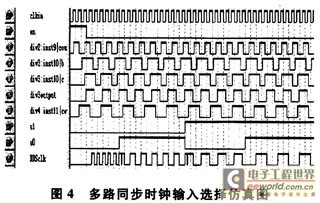

同步逻辑实现多通道波形产生控制模块的同步控制。信号产生通道的工作状态有闲置、异步工作和同步工作3种状态,由用户提供的同步控制命令决定。当波形产生控制命令加载到输出寄存器后,在接收到“准备好”命令后同步逻辑控制指定通道同步的输出控制命令。设计要求各通道具有独立产生信号的能力,且任意通道间可实现同步操作。首先由同步逻辑产生2分频、3分频和4分频电路分别同步2路、3路和4路的信号输入,只有1路信号输出时采用串行时钟即可。然后根据用户同步通道控制命令,控制多路选择通道输出相应的同步时钟。采用同步时钟选择方法设计的多路同步时钟仿真图如图4所示。

从图中可见,2位的同步时钟控制地址s1、s0控制着同步时钟DDSclk的输出。当地址位s1和s0分别为00、01、10和11时,同步时钟DDSclk分别输出了串行时钟和串行时钟2分频、3分频与4分频。其中2分频和4分频通过对串行时钟计数跳转即可实现,方法简单且效果良好。对于3分频的实现则要复杂一点,方法是通过将2个占空比不为50%的3分频信号相与得到1个占空比为50%的时钟输出,如图中div3:inst10/b与div:inst10/c相与得到的3分频时钟输出div3output。

3.2.3 信号产生和调理输出

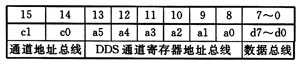

信号产生和调理输出部分的作用是通过接收控制命令对各通道的DDS电路进行控制。经过FIFO缓冲的16位来自用户的控制命令FIFO_DATA,由数据控制部分识别、解析、校验后传输到数据串/并转换模块,串/并转换模块按照数据格式的要求将其转换为2位通道地址总线部分(c1,c0)、6位DDS寄存器地址总线部分(d5~d0)和8位数据总线部分(d7~d0),组成16位控制字,如下所示:

由2位的通道地址选中命令接收通道,6位的DDS寄存器地址总线输出后控制AD9854的寄存器的0x00~0x27单元,8位的数据总线传输波形产生信息和增益控制信息。其中6位的地址总线除了作为DDS寄存器地址外,还用于同步状态的设置。当地址总线为0x3F时,控制器进入同步设置状态,此刻的8位数据总线用于传输同步设置内容。图5为并行多通道波形产生模块的部分状态转换图。

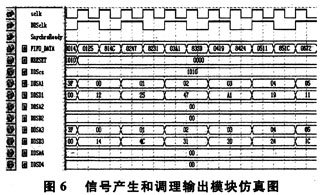

图6为信号产生和调理输出模块的逻辑仿真图,图中DDSA1~DDSA4为6位的DDS寄存器地址总线,DDSD1~DDSD4为8位的数据总线,DDSclk为同步时钟。通过同步设置,选择了1、3通道输出波形,并使DDSclk输出串行时钟的2分频。从图中可看出,此次是对1、3通道进行信号产生的控制,而没有对2、4通道进行操作。同时将16位的FIFO_DATA控制命令译码后输出,图中FIFO_DATA的0x0125经译码后,选中通道1,并驱动DDSAl输出0x01,DDSD1输出0x25。

4 模块测试

首先对各通道的信号产生电路进行单独的测试,然后任意选择2路通道产生独立的激励信号,再分别选择3路和4路通道进行测试。进行以上测试测得模块各通道间异步工作正常,而后进行通道同步测试。设置多通道波形产生模块16位控制字中的a[5:0]为0x3F,进入同步设置模块,设置通道选择和通道输出频率后,对同步通道进行测试,测得同步通道模块工作正常,满足设计要求。

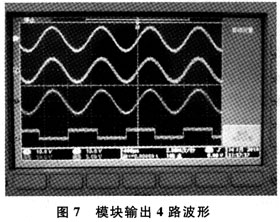

图7为7个通道同时输出波形的测试,其中1、2、3通道为同步方式输出的3路正弦波,4通道为独立输出的方波。测试后发现,模块具备产生高质量的并行多通道激励信号的能力。

结 语

本文以并行多通道信号产生模型为依据,设计并实现了以FPGA为核心器件的并行多通道信号产生模块,主要包括FPGA系统设计和多通道波形产生模块设计。通过模块测试后发现,该模块具备产生高质量并行多通道激励信号的能力。在后续的研究中,以产生各种复杂的激励信号为主,并通过增加并行算法或采用多嵌入式软核等方法改善模块通道之间的并行机制,充分挖掘各通道的并行特性。

并行测试FPGA激励信 相关文章:

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)