FPGA与多核CPU如何改变嵌入式设计

随着嵌入式器件在过去数十年来的爆炸性成长,使得硬件组件及软件工具都有显著的改善。虽然有着这种成长与创新,但传统嵌入式系统的设计方法却少有进步,并逐渐变成一种障碍。有鉴于新标准与协议的快速发展,以及对产品上市压力的日益增加,嵌入式系统设计也即将发生颠覆性的典范改变。

随着硬件技术及软件工具的进步在加速成长,由整合所带来的挑战也开始浮现。如果无法妥善处理这些挑战,将会使得终端产品变得更加昂贵,并且有碍于让更多创新设计的实验、成长及上市。

标准的嵌入式架构

在一般的计算市场,标准化已带来更加稳健而耐用的操作系统、更精炼的终端应用,及基础硬件组件的进步。我们从其中所学到的经验是,从避免花在客制化硬件架构及相关软件组件的努力所省下来的时间,将可获得更佳的解决方案,这可加快上市的时间。

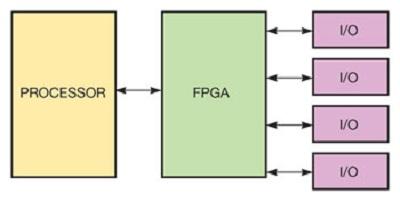

在嵌入式领域,一个相对应的标准架构应该要具有足够的灵活性,以容纳不同的使用案例,同时还要能提供一条可以更新的途径。有鉴于这些限制,在嵌入式领域中的标准,最为稳健而耐用的架构是将一颗微处理器与FPGA相互搭配一起工作,有如一体般(图A)。这两者结合在一起,将可实现显著的设计灵活性。

图A:在图中的标准硬件架构中,处理器与FPGA的结合可实现灵活性,同时也让标准化可以利用较高阶的工具,以便在设计流程中获得显著的效益。处理器可让现有的码链接库重复使用,而FPGA则可让客制化的算法具有灵活的实现方式。

FPGA可带来硬件决定性及可靠性的效益,而不会有ASIC设计突出的成本及缺乏弹性。此外,在FPGA的结构中加载新的逻辑及重新定义链接,让它可以让工程师实现不会过时的设计,且有更为稳健的更新路径,而不需要在硬件上进行大幅的修改。

在嵌入式系统设计中结合处理器与FPGA的情况,在许多产业中已是愈来愈普及。嵌入式系统的设计开发工程师都在使用基于多个处理器及FPGA的设计。其中,FPGA用来执行精准且高速的量测,或运行时间关键的算法。同时处理器则是用来执行实时的操作系统,以处理低频控制回路及提供连至其他分布式结点的以太网络通讯及促进远程数据的存取、系统的管理及诊断。

高阶工具

标准架构所带来的一项关键性效益是,有更多功能强大且优化的高阶工具可以发展和使用,以进行设计。较高阶的工具让某一领域内的专家可以更小及更有效率的设计团队深入嵌入式系统设计。因此,更小规模的设计团队便可将更为复杂的产品推出上市。

效率

以较高阶的设计工具及语言进行应用发展可获得效率,一般通用的计算可为此一效率提出证明。毫无意外地,嵌入式市场将开始目睹高阶设计工具的成长,其中包括Xilinx AutoESL C-to-Gates高阶合成工具、Mentor Graphics Catapult C合成工具及NI LabVIEW最终系统设计软件等。

- Windows操作系统多核CPU内核线程管理方法(01-21)

- 基于DSP和XC2S50嵌入式结构的便携数字存储示波表设计(06-06)

- ARM11和DSP协作视频流处理技术3G视频安全帽设计(02-15)

- Xilinx FPGA的嵌入式系统开发过程(12-06)

- 应对汽车电子嵌入式设计的若干挑战(12-03)

- 基于DSP和VxWorks的RTOS视频网络检测系统(11-18)