嵌入式系统VGA显示接口的系统实现,软硬件解决方案

- 设计摘要

在许多嵌入式系统中,为了实现良好的人机界面,这就对系统的MCU和显示设备提出了更高的要求。若能用低速的MCU实现和PC机类似的显示效果,将会大幅度提高产品的附加值。目前,带有VGA接口和类VGA的显示设备随处可见,若能以此类设备作为各种嵌入式系统的显示器,也可提高各种嵌入式设备人机界面的通用性。本项目采用FPGA器件和带有VGA接口的显示器,实现适用于各种嵌入式系统的显示接口,使得低速的MCU不需要增加过多开销即可采用VGA接口设备作为显示器。

- 硬件结构图

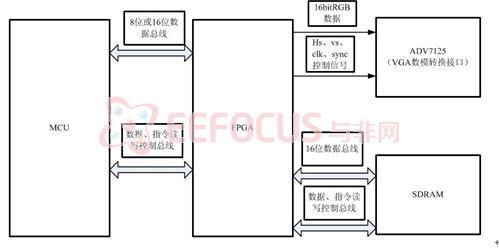

系统硬件结构图如图1所示:

图1系统硬件结构图

三、软件介绍

系统软件分为两个部分:MCU软件模块和FPGA软件模块。MCU软件模块主要负责将要显示数据传送给FPGA,主要实现的功能是在VGA显示器上打点(在指定的行坐标、列坐标出以某一指定的颜色显示一个点),在此功能的基础之上实现划线、矩形填充、显示图片的功能。FPGA模块主要负责接收MCU模块发送的数据,并将接收到的数据通过内部的写FIFO单元存入外接的SDRAM存储器中,然后再通过内部的读FIFO单元从SDRAM中将数据取出送到VGA数模转换模块,同时FPGA模块还要提供VGA显示所需要的HS、VS、SYNC等扫描信号。

1、FPGA软件模块介绍

FPGA模块的软件主要有以下几部分组成。

- FPGA顶层模块:

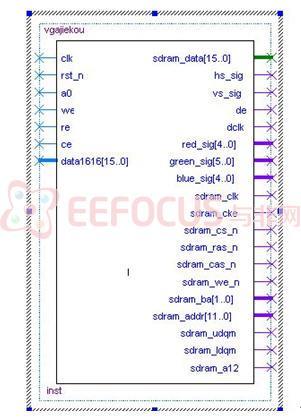

FPGA顶层模块主要定义了FPGA与外围的MCU、SDRAM、VGA数模转换的接口。各引脚的具体定义如表1和图1所示。

表1

方向 | 名称 | 描述 |

Input | clk | 输入时钟50M |

Input | rst_n | 异步复位,低有效 |

Input | a0 | 数据地址选择,低表示地址 |

Input | we | 写信号,上升沿有效 |

Input | re | RE,读信号,下降沿有效 |

Input | ce | 片选,低有效 |

input | [15:0]data1616 | 时序接口,数据线 |

output | dclk | 输出时钟40M,给VGA |

output | hs_sig | 列同步信号 |

output | vs_sig | 行同步信号 |

output | red_sig[4:0] | 红信号 |

output | green_sig[5:0] | 绿信号 |

output | blue_sig[4:0] | 蓝信号 |

output | sdram_clk | SDRAM时钟信号 |

output | sdram_cke | SDRAM时钟有效信号 |

output | sdram_cs_n | SDRAM片选信号 |

output | sdram_ras_n | SDRAM行地址选通脉冲 |

output | sdram_cas_n | SDRAM列地址选通脉冲 |

output | sdram_we_n | SDRAM写允许位 |

output | sdram_ba[1:0] | SDRAM的L-Bank地址线 |

output | sdram_addr[12:0] | SDRAM地址总线 |

inout | sdram_data[15:0] | SDRAM数据总线 |

output | sdram_udqm | SDRAM高字节屏蔽 |

output | sdram_ldqm | SDRAM低字节屏蔽 |

图1 FPGA软件顶层模块

- SDRAM读、写控制模块

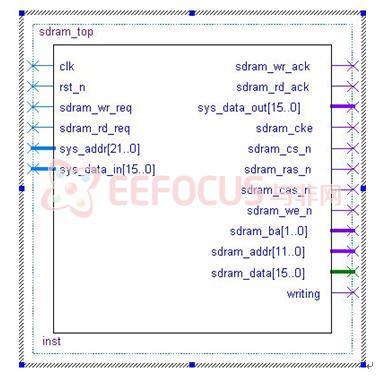

SDRAM读、写控制模块主要实现FPGA对SDRAM存储器的读写控制,该模块主要完成SDRAM的上电初始化以及定时刷新、读写控制等状态的变迁。该模块各引脚的具体定义如表2和图2所示。

表2

方向 | 名称 | 描述 |

input | clk | 系统时钟,100MHz |

input | rst_n | 复位信号,低电平有效 |

input | sdram_wr_req | 系统写SDRAM请求信号 |

input | sdram_rd_req | 系统读SDRAM请求信号 |

output | sdram_wr_ack | 系统写SDRAM响应信号 |

output | sdram_rd_ack | 系统读SDRAM响应信号 |

input | sys_addr[21:0] | 读写SDRAM时地址暂存器 |

input | sys_data_in[15:0] | 写SDRAM时数据暂存器 |

output | sys_data_out[15:0] | 读SDRAM时数据暂存器 |

output | writing | SDRAM正写标志 |

output | sdram_clk | SDRAM时钟信号 |

output | sdram_cke | SDRAM时钟有效信号 |

output | sdram_cs_n | SDRAM片选信号 |

output | sdram_ras_n | SDRAM行地址选通脉冲 |

output | sdram_cas_n | SDRAM列地址选通脉冲 |

output | sdram_we_n | SDRAM写允许位 |

output | sdram_ba[1:0] | SDRAM的L-Bank地址线 |

output | sdram_addr[11:0] | SDRAM地址总线 |

inout | sdram_data[15:0] | SDRAM数据总线 |

图2 SDRAM顶层模块

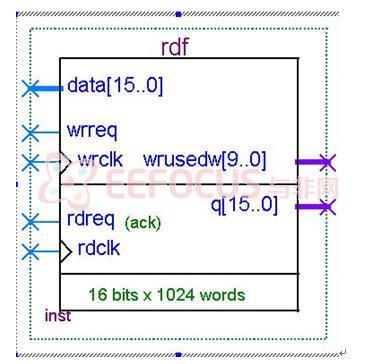

- 读、写FIFO模块

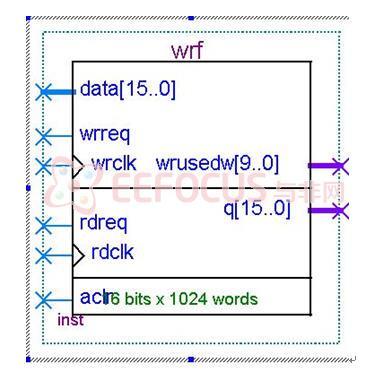

读、写FIFO模块采用系统的IP核实现,FIFO的容量为1K字单元(16位)。Wrf FIFO单元在wrreq为1时将MCU的数据存入wrf

FIFO,数据存入后,立即被写入SDRAM中。Rdf FIFO单元在rdreq为1时将数据从SDRAM中取出送给VGA控制模块。

图3 写FIFO模块

图4 读FIFO模块

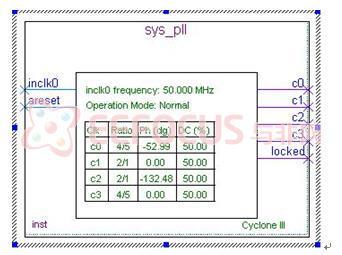

- PLL单元

PLL单元主要负责管理系统所需的各种时钟信号,其中主要有:inclk0为系统输入时钟(50MHZ)。c1、c2为SDRAM提供100MHZ的读、写时钟。c0、c3分别是为采样MCU数据和VGA时序扫描所提供的40MHZ时钟。

图5 PLL模块

- VGA控制模块

VGA控制模块主要负责将从MCU接收到的数据送给wrf FIFO中,然后从rdf FIFO中取出要显示的数据,并产生VGA所需的行扫描、列扫描信号、同步信号、时钟信号,一并送给外围的VGA数模转换电路。该模块的各引脚的具体定义如表3和图6所示。

表3

方向 | 名称 | 描述 |

input | clk_40m | 输入时钟40M |

input | clk_100m | 输入时钟100M |

input | rst_n | 异步复位,低有效 |

input | a0 | 数据地址选择,低表示地址 |

input | we | 写信号,上升沿有效 |

input | re | 读信号,下降沿有效 |

input | ce | 片选,低有效 |

input | rdf_q[ |

- 基于DSP Builder的VGA接口设计(04-10)

- μC/GUI在基于NiosⅡ嵌入式开发平台的环境智能监控系统中的移植与应用(01-14)

- 基于DSP Builder的VGA接口系统设计(04-10)

- 基于FPGA的LCDVGA控制器设计(06-06)

- 利用FPGA实现外设通信接口之: 典型实例-VGA接口的设计与实现(06-05)

- 利用FPGA实现外设通信接口之: 利用FPGA实现常用显示接口(Display Interface)(06-05)