拿来即用,指纹识别保密系统完整解决方案

15 枚 | |

图像分辨率 | 500dpi |

平均匹配速度 | 1 秒 |

抗静电能力 | IEC61000-4-2 标准 15KV |

抗磨损强度高 | 1 百万次 |

峰值耗电 | 150mA |

工作环境温度 | -10°C 至 70°C |

最大工作湿度 | 98% |

工作电压 | 3.3V |

尺寸 | 4.4 x 6.6 cm |

7.3 VHDL 实现的 AES 加密模块的测试

测试方案

National Institute of Standards and Technology (NIST) 发布 AES 标准的文档Announcing the ADVANCED ENCRYPTION STANDARD (AES) 中,以附录的形式给出了一组 128 位密钥的加解密数据。我 们选择 ISE Simulator 为仿 真器,将这组数据的明文与密钥作为 输入,看加密后的结果是否正确。再将加密结果作为输入,看解密后是否为原文。

测试数据

数据来自于 NIST 发布的联邦信息处理标准(FIPS PUBS) 197 。

明文:00112233445566778899aabbccddeeff

密钥:000102030405060708090a0b0c0d0e0f

密文:69c4e0d86a7b0430d8cdb78070b4c55a

结果分析

在 ISE Simulator 提供的可视化波形输入编辑平台 TBW(Test Bench Waveform)下,编辑仿真波形。其中密钥部分:

明文部分:

加密结果:

密文为

69c4e0d86a7b0430d8cdb78070b4c55a,与文档中给出的完全一样,说明加密电路正确。将密文 69c4e0d86a7b0430d8cdb78070b4c55a 作为输入,进行解密仿真,仿真结果为:

与输入的明文一样,说明 AES 模块能够进行正确的加解密操作。

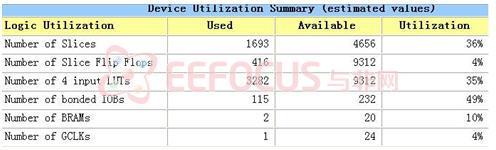

下面是 ISE 中 AES 模块编译后的资源消耗情况如表 7-2。

表 7-2 AES资源消耗表

其中逻辑资源使用了 1688 Slices,占整个可用资源的 36%,存储资源用了 2 块 RAM,占全部可用量的 10%。关于 AES 的 VHDL 实现已经有了不少研究成果,在此做一个比较。电子科技大学的刘珍桢在其硕士论文《AES 加、解密算法的 FPGA 优化设计》一文中介绍了他的设计。他的设计是基于 ATERA 公司的 Stratix 系列 FPGA 芯片,在 QUARTUSII 环境下实现的。资源消耗情况如下:

Total logic elements: 30626

Total memor y bits: 231544.

将本模块同样放到 QUARTUSII 环境下进行编译,资源消耗情况如下:

通过比较发现,本模块 在资源消耗方面有明显的优势,这是以牺牲加解密速 度获得的。

刘珍桢的设计中,每 5 个时钟周期即可完成一次加密或解密运算,而本模块则需要 80 个时钟周期。本模块在 50MHz 的系统时钟下,最高可达 10MByte/s 的加解密速度,完全能够满足需求。由 此可 见 ,AES 模 块 的设 计 在速 度与 资 源消 耗 上取 得了 很 好的 平 衡。 既适 当利 用 了FPGA 片上资源,也很好满足了应用需求。

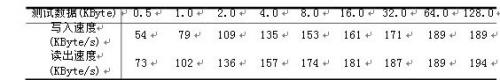

7.4 作品整合测试

将作品插到电脑 USB 端口,再将 U 盘连接到本作品。在正确输入指纹之前,电脑不显示 U 盘盘符。正确输入指纹后,开始显示盘符,电脑与 U 盘可以正常通信。传输速率测试结果如下表:

再将加密后的文件重新 拷贝到电脑上,打开后与原文件一样,作 品加解密运算正确。将加密后的 U 盘直接连到电脑上,电脑无法读写 U 盘中的数据。

通过以上测试,作品完全能够正确完成加解密运算,有效识别指纹,为 U 盘提供可靠的保护,完全实现了预期目标。

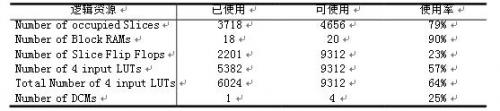

7.5 开发板资源资源利用情况

本 作 品 充 分 利 用 了 开 发 板 上 的 资 源 。 FPGA芯 片 、 Platform Flash 、 LCD显 示 屏、push-button switchesHirose FX2 、expansion connector 等资源得到了合理利用,并且开发了外扩电路板。其中,FPGA 芯片内部自用利用率见下表:

8 作品功能特色与应用前景

8.1 功能特色与创新

完全靠硬件实现,通用性好,无需为 PC 编写任何驱动或应用程序,同样也没有上传任何程序到 PC 执行,理论上对所有普通 U 盘和支持 USB 协议的操作系统均适用。采用磁盘分区加密技术,安全性高于普通的文件加密技术。采用 AES 加密标准。VHDL 逻辑模块实现 AES,加解密速度快。由指纹特征产生密钥,安全强度高,用户使用方便。作品可同时存储多个指纹,可同时服务于多个用户,节约成本。作品与 U 盘分离,安全管理更可靠。

8.2 技术难点

在作品的完成过程中,我们遇到并解决了以下难点:

1 USB 协议解析

2 AES 的 VHDL 实现,权衡资源利用率和加解密速度

3 磁盘分区加密技术在本作品中的应用

4 设备对各种 U 盘的通用性

8.3 应用前景

作品拥有广阔的应用前景,能为私人、企业、政府等机构提供便捷、可靠的 U 盘安全解决方案。加密器与 U 盘相分离,减小指纹信息泄露的威胁,在需要保密的部门更便于安全上的管理,因此将大受欢迎。

指纹识别 保密系统 Spartan3E FPGA XC3S500E 相关文章:

- 基于DSP CCS 2.2实现指纹识别预处理系统(07-28)

- 基于FPS200传感器和DSP的指纹识别系统(01-12)

- 基于嵌入式Linux平台的指纹门禁系统(01-20)

- 基于DSP CCS2.2实现指纹识别预处理系统设计(06-10)

- 基于DSP CCS2.2实现指纹识别预处理系统设计方案(06-17)

- 基于DSP的指纹识别系统设计方案(07-03)