100MHz 数字存储示波表样机的研究与试制----数据采集系统设计(一)

K FIFO读使能都置为无效,写入的数据直接存入0.5K的FIFO不再转移,直到2.5K全部写满为止。2.读FIFO时,初始状态为0.5K FIFO读使能有效,2K FIFO读写使能同时有效。来一个读时钟就从2K FIFO读走一个最老的数据,同时,又从0.5K FIFO写进一个数据。当0.5K FIFO读空后,即0.5K FIFO的数据已全部转移至2K FIFO后,0.5K FIFO读空信号有效,从而,关断2K FIFO的写使能,使2K FIFO只读不写,直到所有2.5K数据全部读空。

3.3触发

触发是由触发电路来实现的。如果没有触发电路,你在屏幕上看到的将会是具有随机起始点的很多波形杂乱重叠的图像。而触发电路的主要作用就是保证每次拿去显示的点都是从输入信号上的一精确确定的点开始。它主要包括:触发源选择、触发类型选择、触发耦合方式选择、触发释抑等。

3.3.1触发电路

1.触发源选择

触发源一般有内触发、外触发和电源触发三种类型。触发源的选择应根据被测信号的特点来确定,以保证被测信号波形的稳定显示。

(1)内触发:将被测信号本身作为触发源。

(2)外触发:用外接的、与被测信号有严格同步关系的信号作为触发源,这种触发源用于比较两个信号的同步关系,或者,当被测信号不适于作触发信号时使用。

(3)电源触发:用50Hz的工频正弦信号作为触发源,适用于观测与50Hz交流有同步关系的信号。

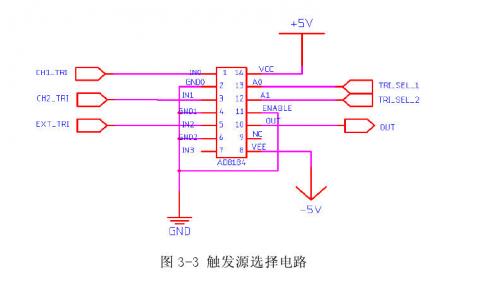

在实际项目中,我们只采用了内触发和外触发两种触发源。它主要通过DSP发出的串行码经过FPGA和D触发器来控制一个四路选择器来实现。具体电路如图3-3.

2.触发耦合方式选择

选择好触发源后,为了适应不同的触发信号频率,示波器一般设有四种触发耦合方式。

(1)“DC”直流耦合:是一种直接耦合方式,用于接入直流或缓慢变化的触发信号,或者频率较低并含有直流分量的触发信号。

(2)“AC”交流耦合:是一种通过电容耦合的方式,有隔直作用。触发信号经一个电容接入,用于观察从低频到较高频率的信号。

(3)“低频抑制”耦合:使触发源信号通过一个高通滤波器以抑制其低频成分。

这对于显示包含很多电源交流噪声的信号是很有用的。

(4)“高频抑制”耦合:使触发源信号通过低通滤波器以抑制其高频分量。这意味着既使一个低频信号中包含很多高频噪声,我们仍能使其按低频信号触发。

3.触发类型选择

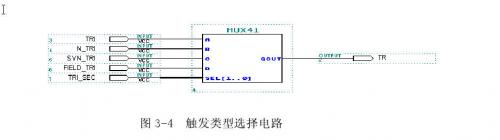

数字存储示波器最大的优点就是具有先进、多样的触发功能,从而使示波器的应用更加得心应手。利用这些触发功能,示波器就能完成比以前更多的工作。常用的触发类型有边沿触发、视频触发、脉冲触发和毛刺触发。本项目中采用了边沿触发和视频触发。其中,边沿触发分为上升沿触发和下降沿触发两种;视频触发分为行频触发和场频触发两种。这四种触发信号分别进入FPGA,通过一个四路选择器,选择其中之一作为系统触发信号。其具体电路如图3-4.

4.触发释抑

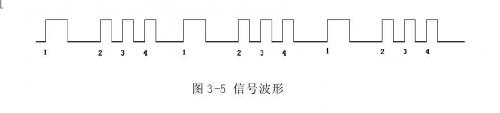

触发释抑的主要作用就是调整触发信号为一标准的周期信号,从而达到稳定显示波形的目的。例如,我们要观测如图3-5所示的周期信号。这个信号波形一个周期内的1、2、3、4点的位置都满足触发条件。如果按一般情况,系统

就会在1、2、3、4点都产生触发信号,这样就会造成显示时波形的左右抖动。

解决这一问题的关键就是在于调节触发释抑时间,使触发信号产生在每个信号波形周期的相同位置,即,使每次触发都发生在各周期的1、2、3或4位置,这样,信号波形才能无抖动的重现出来。

本项目中触发释抑具体实现电路如图3-6所示。由图知,这个电路包括三

个输入信号:计数使能信号PRE_TRI_FULL;计数时钟信号CNT_CLK;释抑时间设置TRI_DELAY_DATA.一个输出信号:触发屏蔽信号Armed.它的工作原理是:刚开始时Armed为低电平,屏蔽所有触发信号。达到预触发深度后,计数使能信号PRE_TRI_FULL有效,使计数器按照计数时钟CNT_CLK开始计数。当计数到预先设置的计数值TRI_DELAY_DATA后(此计数值由DSP送过来),Armed变为高电平,开放触发信号。

- 100MHz 数字存储示波表样机的研究与试制----DSP 芯片的连接与配置(一)(06-04)

- 基于DSP和XC2S50嵌入式结构的便携数字存储示波表设计(06-06)

- 基于DSP和USB的三维感应测井数据采集系统(06-14)

- 基于DSP的USB口数据采集分析系统设计(09-22)

- 基于Linux平台的天气雷达高速数据采集系统设计(03-13)