基于CPLD器件的单稳态脉冲展宽电路

为另一个相同脉宽控制电路的计数器的时钟脉冲。

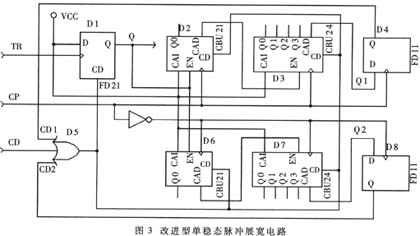

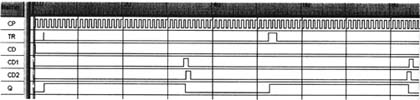

这样,如果输入的窄脉冲在时钟脉冲的前半周期内到达,则由D6、D7、D8组成的脉宽控制电路先开始计数;如果输入的窄脉冲在时钟脉冲的后半周期内到达,则由D2、D3、D4组成的脉宽控制电路先开始计数。由于上下两个脉宽控制电路的时间计数值是相同的,故先计数则先结束,后计数则后结束。两者之差为半个时钟周期值。展宽脉冲信号的宽度,始于输入窄脉冲的前沿,而止于两个脉宽控制电路中最早结束定时计数的那个计数器的进位脉冲所产生的清零脉冲信号。因此,不管输入窄脉冲信号的前沿与时钟脉冲的相对时间关系如何,其输出展宽脉冲的宽度为脉宽控制电路的时间计数值与输入窄脉冲的前沿加上时钟脉冲的前沿或后沿之差。尽管脉宽控制计数电路的时钟脉冲周期没有改变,但由于输入窄脉冲的前沿与控制计数电路时钟脉冲上升沿的最大时差只有半个时钟脉冲周期(注意:时钟脉冲信号的占空比为1:1),故展宽脉冲信号的宽度误差小于"+"或-半个时钟脉冲周期。图4是图3所示电路的时序仿真波形图。

从时序仿真波形图中可以看到,前、后两个输入窄脉冲的前沿与对应的 展宽脉冲信号的前沿之间的延迟时间是一样的。而展宽脉冲信号的后沿总是与两个脉宽控制计数电路中最先结束计数的那个计数器的进位脉冲所产生的清零 脉冲信号相对应的。从而证实了采用图3所示电路所产生的脉冲信号的宽度精确度较图1所示之电路几乎提高一倍。在外部条件不变的情况下,提高展宽脉冲信号精度的方法有多种,这里不再一一例举。

在CPLD器件中,可以将输入的窄脉冲展宽;当然,亦可以将输入的宽脉冲变窄;或使其具有象54HC123单稳态触发器那样的延时和可重触发功能。用CPLD器件可以实现常用单稳态电路的功能;用FPGA器件,同样可以实现上述功能。采用何种器件何种方法,主要看电路设计的技术指标,设计者所具有的设计环境和周围电路中所使用器件的类型。总之,随着大规模集成电路产品性能的不断提高、体积的不断减小和成本的不断降低,基于CPLD器件设计的单稳态电路的性能将大大提高,这种单稳态电路的应用亦将越来越广泛。

- 基于DSP应用于线切割机床的脉冲电源设计(02-01)

- TMS320C6701DSP线性调频信号数字脉冲压缩(05-23)

- 基于DSP与CPLD的三相五电平变频器PWM脉冲发生器(08-01)

- 基于DSP正弦波调制的三电平变换器(02-05)

- 基于DSP与CPLD的变频器PWM脉冲发生器设计(03-06)

- 基于dsPIC30F的脉冲氙灯驱动系统的设计方案(04-16)