VHDL设计中电路优化问题

2 优化系统速度的VHDL设计策略

选用基于VHDL设计的CPLD/FPGA器件往往首先是为了满足高速运行的需要,如通信系统。系统运行速度与电路节点之间的延时直接相关,因此,减少冗余逻辑,缩短节点延时是提高系统速度的关键。速度优化与电路结构设计(如器件结构特性、系统电路构成和PCB制板情况)和软件使用(如综合器性能和 VHDL描述方式)都有关系。

2.1 电路结构方面速度优化的主要方法

① 流水线设计是最常用的速度优化技术。采用流水线设计虽然不能缩短总工作周期,但通过把一个工作周期内的逻辑操作分成几步较小操作,并连续同步实现的策略,可大大提高系统总体运行速度。

② 合理使用嵌入式阵列块EAB资源和LPM宏单元库。在DSP、图像处理等领域,乘法器是应用最广泛、最基本的模块,其速度往往制约着整个系统性能。而EAB是PLD器件中非常有效的高速资源,利用EAB单元和参数化模块LPM,可以设计出乘法器等高速电路。

③ 关键路径优化。所谓关键路径是指从输入到输出延时最长的逻辑通道。关键路径优化是保证系统速度优化的有效方法。

2.2 软件使用方面速度优化的方法

一般EDA软件尤其是综合器,均会提供一些针对具体器件和设计的优化选项。设计者在使用软件时应注意根据优化目标的要求,适当修改软件设置。在MAX+plusII中,就可以使用Assign/Device命令选择不同速度等级的芯片。

3 面积优化的VHDL设计策略

面积优化是提高芯片资源利用率的另一种方法,通过面积优化可以使用规模更小的芯片,从而降低成本和功耗,为以后技术升级预留更多资源。面积优化最常用的方法是资源共享和逻辑优化。

3.1 资源共享方法

资源共享的主要思想是通过数据缓冲或多路选择的方法来共享数据通道中占用资源较多的模块(如乘法器、多位加法器等算术模块)。

例程3: process(A0,A1,B,sel)

begin

if(sel=‘0’)then result=A0*B;

else result=A1*B;

end if;

end processs;

例程4: process(A0,A1,B,sel)

begin

if(sel=‘0’)then temp=A0;

else temp=A1;

end if;

result=temp*B;

end processs;

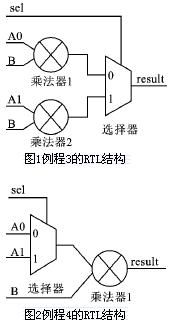

例程3的设计可用图1描述,例程4的设计可用图2描述。可见例程4节省了一个代价高昂的乘法器,整个设计占用面积比例程3几乎减少了一半。

3.2 逻辑优化方法

通过逻辑优化以减少资源利用也是常用的面积优化方法(如常数乘法器的应用,并行逻辑串行化处理等),但其代价往往是速度的牺牲。在延时要求不高的情况下,采用这种方法可以达到减少电路复杂度、实现面积优化的目的。

4 结论

通过以上初步的探讨可知,用VHDL进行集成电路的设计,不仅需要熟悉VHDL语言的使用方法和对设计要求的深刻理解,而且应在设计全程中遵循最优化设计的基本原则,在电路结构设计和软件使用中寻找满足设计要求的最佳方案。

- DSP HPI口与PC104总线接口的FPGA设计(04-14)

- 基于FPGA的AD7862接口电路设计(01-01)

- 基于VHDL的感应加热电源数字移相触发器设计方案(03-20)

- 单板嵌入式硬件平台SingleBoard RIO(03-19)

- 设计嵌入式系统时选用NI LabVIEW的10大理由(03-19)

- 功能原型设计系列:为什么要进行快速原型(03-22)