基于VHDL+FPGA的自动售货机控制模块的设计与实现

,次态不同

ELSIF state_inputs《=“01” THEN next_state《=S1;

ELSIF state_inputs《=“10” THEN next_state《=S2;

END IF;

WHEN S1=》comb_outputs《=“00”; --现态S1

IF state_inputs《=“00” THEN next_state《=S1; --输入不同,次态不同

ELSIF state_inputs《=“01” THEN next_state《=S2;

ELSIF state_inputs《=“10” THEN next_state《=S3;

END IF;

WHEN S2=》comb_outputs《=“00”; --现态S2

IF state_inputs《=“00” THEN next_state《=S2; --输入不同,次态不同

ELSIF state_inputs《=“01” THEN next_state《=S3;

ELSIF state_inputs《=“10” THEN next_state《=S4;

END IF;

WHEN S3=》comb_outputs《=“10”; --现态S3

IF state_inputs《=“00” THEN next_state《=S0; --输入不同,次态不同

ELSIF state_inputs《=“01” THEN next_state《=S1;

ELSIF state_inputs《=“10” THEN next_state《=S2;

END IF;

WHEN S4=》comb_outputs《=“11”; --现态S4

IF state_inputs《=“00” THEN next_state《=S0; --输入不同,次态不同

ELSIF state_inputs《=“01” THEN next_state《=S1;

ELSIF state_inputs《=“10” THEN next_state《=S2;

END IF;

END CASE;

END PROCESS;

END state;

编译、仿真及FPGA实现

在Altera公司的可编程逻辑器件集成开发平台Quartus II 8.0下完成程序的编辑、编译并进行时序仿真。

1)编译:编译是EDA设计中的核心环节。软件将对设计输入文件进行逻辑化简、综合和优化, 适当地用一片或多片器件进行适配,最后产生编程用的编程文件。主要包括设计编译和检查、逻辑优化和综合、适配和分割、布局和布线、生成编程数据文件等过程。自动售货机控制模块VHDL文件编译报告如图2所示。

图2 编译报告

报告中给出了进行编译的时间、采用的开发软件的版本、顶层设计实体名、选用器件的系列和型号、时序分析情况、占用资源情况及引脚使用情况等信息。

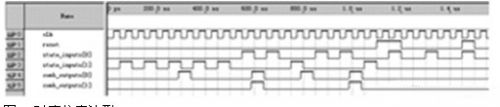

2)时序仿真:编译后对系统和各模块进行时序仿真,分析其时序关系,估计设计的性能及检查和消除竞争冒险是非常有必要的。仿真前,先利用波形编辑器建立波形文件,仿真结果将会生成报告文件和输出信号波形,从中便可以观察到各个节点的信号变化。若发现错误,则返回设计输入中修改设计逻辑。自动售货机控制模块仿真波形如图3所示。

图3 时序仿真波形

3) FPGA实现:将编译阶段生成的编程数据文件通过Quartus II 下载到芯片EPF10K10LC84-4中,并在电子设计自动化实验系统中进行测试得到了正确的结果。

- DSP HPI口与PC104总线接口的FPGA设计(04-14)

- 基于FPGA的AD7862接口电路设计(01-01)

- 基于VHDL的感应加热电源数字移相触发器设计方案(03-20)

- 单板嵌入式硬件平台SingleBoard RIO(03-19)

- 设计嵌入式系统时选用NI LabVIEW的10大理由(03-19)

- 功能原型设计系列:为什么要进行快速原型(03-22)