基于流水线CORDIC算法的正交幅度调制解调在FPGA上的设计实现

0 引言

正交幅度调制是频率利用率很高的一种调制技术。与其他调制技术相比,具有能充分利用带宽、抗噪声能力强等优点,在移动通信、有线电视传输和ADSL中均有广泛应用。它的载波信号的FPGA实现一般采用DDS(直接数字频率合成)技术,即在两块ROM查找表中分别放置一对正交信号。通过这种方法虽然可以输出一组完全正交的载波信号,但它主要用于精度要求不是很高的场合,如果精度要求高,查找表就很大,相应的存储器容量也要很大,使系统的运行速度受到限制,不适合现代通信系统的发展。本文基于CORDIC(Coordinate Rotation Digital Computer)算法,研究正交幅度调制解调器的FPGA实现方法。该方法不仅能够节省大量的FPGA逻辑资源,而且能很好地兼顾速度、精度、简单及高效等各个方面。

1 正交幅度调制解调器工作原理

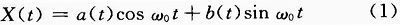

正交幅度调制解调器系统框图如图1所示。其中,a(t)和b(t)为两路相互独立的待传送基带信号,正交信号发生器输出两路互为正交的正弦载波信号,经过两个乘法器可以获得互为正交的平衡调幅波,即不带载频的双边带调幅波。假设乘法器的乘法系数为1,则经过加法器产生的调制信号为:

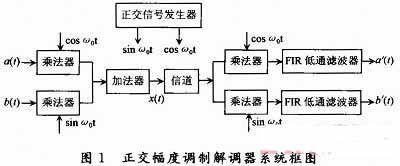

对调制信号X(t)进行解调,采用了正交同步解调方法。已调正交调幅信号X(t)分别与正交信号发生器产生的余弦信号和正弦信号相乘后产生两路输出信号:

2 正交信号发生器的设计

2.1 CORDIC算法原理

CORDIC算法是由J.Volder于1959年提出的。该算法适用于解决一些三角学的问题,如平面坐标的旋转和直角坐标到极坐标的转换等。 CORDIC算法的基本思想是通过一系列固定的、与运算基数有关的角度的不断偏摆,以逼近所需的旋转角度。从广义上讲,CORDIC方法就是一种数值计算的逼近方法。该算法实现三角函数的基本原理如下:

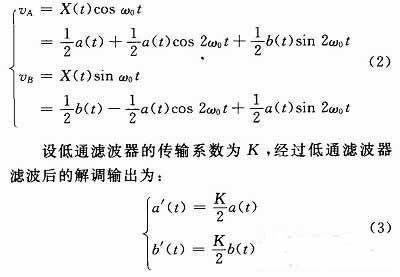

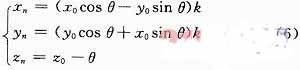

设初始向量(x0,y0)逆时针旋转角度口后得到向量(xn,yn),则:

式中:θi表示第i次旋转的角度,并且tanθi=2-i;zi表示第i次旋转后与目标角度的差;δi表示向量的旋转方向由zi的符号位来决定,即δi=sign(zi);为每一级的校正因子,也就是每一级旋转时向量模长发生的变化,对于字长一定的运算,总的校正因子是一个常数。迭代n次(n→∞)后可以得到如下结果:

当给定的初始输入数据为x0=1/k,y0=0时,z0=θ,则输出为:

由上可知,xn,yn分别为输入角θ的余弦和正弦值,故基于CORDIC算法可产生正交信号。

2.2 CORDIC算法流水线结构

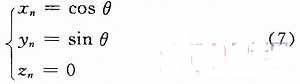

由式(5)可以看出,CORDIC算法的实现只需要基本的加减法和移位操作,因此很容易用硬件实现。该硬件的实现可以通过图2所示的基本单元级联成流水线结构实现。在经过n(迭代次数)个时钟的建立时间之后,每隔一个时钟便能输出一个运算结果。输出精度由CORDIC算法中的迭代次数决定。如需提高精度,只需简单地增加流水单元即可,扩展性很好,而且这并不会大量增加FPGA的资源耗费。

3 FIR低通滤波器设计

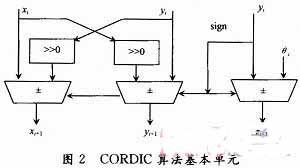

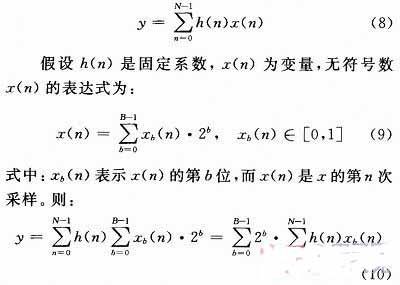

FIR低通滤波器设计可以采用分布式算法,利用FPGA查找表代替乘法器来实现。为便于理解分布式算法的原理,考虑“乘积和”内积如下:

式(10)的形式被称为分布式算法,分布式算法是一种以实现乘累加运算为目的的运算方法。如果建立一个查找表,表中数据由所有固定系数的所有加的组合构成,那么用N位输人数据构成的N位地址去寻址查找表。如果N位都为1,则查找表的输出为N位系数之和;如果N位中有0,则其对应的系数将从和中去掉。这样乘法运算就成了查找操作,整数乘法可以通过左移b位实现。滤波器的系数h(n)可以使用Matlab的FDATool设计工具来获得。

4 调制解调器的FPGA设计

DSP Builder是美国Altera公司推出的一个面向DSP开发的系统级工具,作为Matlab的一个Simulink工具箱,可以帮助设计者完成基于FPGA的DSP系统设计的整个流程。更为重要的是基于Simulink平台利用DSP Builder库进行FPGA设计时,能利用DSP Builder库的HDL Import模块将HDL文本设计转变成为DSP Builder元件,在系统的模型设计中使用,为系统的FPGA设计提供很大的方便。因此,调制解调器的设计采用VHDL文本与Simulink模型图设计相结合的方法。

4.1 子模块的VHDL设计

CORDIC算法和FIR低通滤波器两个子模块可以在QuartusⅡ环境中采用VHDL代码进行设计,也可以基于Simulink平台利用DSP Builder库进行模型图设计。但是用模型图设计时,设计图会显得非常复杂、庞大,不利于阅读和排错,而VHDL代码直接描述会比Simulink模型图描述更为简便。故以上两个模块均在QuartusⅡ环境中,采用VHDL代码进行设计描述及编译。

4.2 系统模型建立

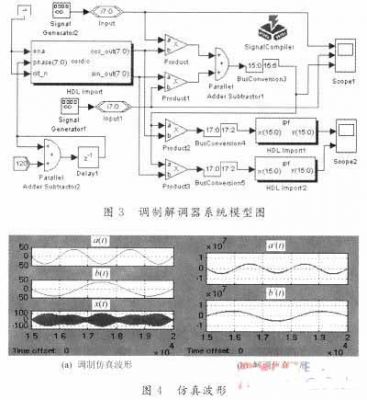

图3为基于Simulink平台建立的调制解调器系统模型图。首先利用Altera DSP Builder库的HDL Import模块将设计的CORDIC算法及低通滤波器子模块对应的文本文件导入,将文本设计转变成为DSP Builder元件模块,然后按图3调用DSP Builder和Simulink库中的其他图形模块建立系统模型图,并设置相应模块参数。

4.3 系统仿真验证与实现

完成模型设计之后,可以基于Simulink平台对模型进行系统仿真,即通过Simulink中的示波器Scope查看仿真结果(见图4)。仿真结果表明,设计电路实现了调制解调功能。然后双击SignalCompiler模块,将模型设计转换成可综合的RTL级VHDL代码,并对其进行综合、配置下载。

- 基于SIMULINK的心电信号源系统设计分析(11-24)

- 使用基于模型的设计进行早期验证和确认(01-25)

- 基于DSPBuilder的FIR滤波器的系统设计(03-19)

- 基于FPGA设计DSP的实践与改进设计(05-11)

- SPWM波控制单相逆变器双闭环PID调节器的Simulink建模与仿真(09-22)

- G.726语音编解码在SoPC系统中(06-06)