多时钟FPGA设计策略阐述

时间:06-05

来源:互联网

点击:

减少时钟数量

根据市场调查,目前还没有哪个FPGA器件能够支持这种多路复用器/解复用器设计所需的40个时钟。所以,我们必须减少所需要的时钟数。

首先了解E2和E3多路复用器的时钟。前面已经分析了4个E2多路复用器工作在相同时钟下的可接受度,E3多路复用器运行于比E2时钟高得多的速率,必需使用一个不同的时钟。但是,如果我们从E3时钟中引出E2时钟是否可行呢?因为E3多路复用器要从每个E2支路得到数据,我们可以在需要E2多路复用器给我们数据时,简单地将脉冲送给每个多路复用器。我们没有去掉任何时钟,但E2时钟现在是基于E3时钟。

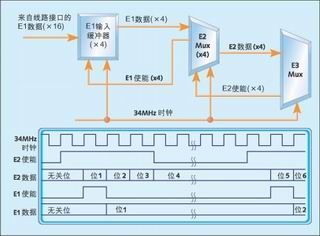

如果在所有的多路复用器中也使用同样的时钟,并且只使用一个使能信号来告诉E2多路复用器什么时候工作,这时会产生什么问题呢?如果E3多路复用器用34.368MHz时钟产生使能信号,在这些使能信号上的抖动不会比用在FPGA中任何其它同步逻辑更大。所以,使能信号可以使用正常(高抖动)布线资源,这样就不需要单独的8.448MHz多路复用器时钟,读取E1数据缓冲器的数据时也是一样。换言之,如果E2多路复用器需要数据,它可以激活到特定缓冲器的使能信号。到缓冲器的时钟本身能够保持E3多路复用器所用的34.368MHz时钟,如图5所示。

最后,我们检查16个从线路接口芯片输入到FPGA的E1时钟。这些时钟有会产生下面几个问题:首先,16个时钟将占用太多可用芯片时钟布线资源;其次,在同一个FPGA中使用16个异步时钟来驱动相互邻近的触发器,由于地弹、串扰和其它效应将产生噪声问题。例如,由于噪声的原因,一个正边沿触发器会在下降边沿时改变输出状态,此类问题将难以处理。

- LTC4312:两通道、二线式总线多路复用器(10-09)

- FPGA设计与DSP设计的区别(12-21)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)