应用VHDL设计通信编码波形

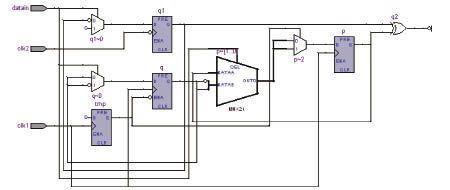

具体VHDL模块图如图12所示。

图12 RZ(单极性归零码)的模块图

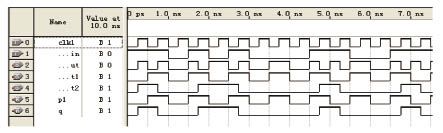

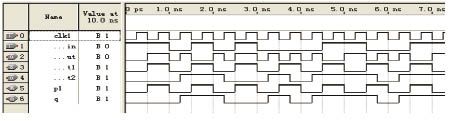

程序在QUARTUSII环境中编译仿真波形如图13所示。

图13 RZ码波形

积分曼彻斯特码

曼彻斯特编码是一种双相码。除了中间发生跳变外,当为“0”时相邻码元电平极性改变,“1”时相邻码元电极性不改变,由于要将输入datain信号中间跳变,故需两个时钟clk1、clk2,且clk1是4分频,clk2是2分频,都在两时钟上升沿遇“0”跳变,遇“1”保持,输出信号encoder-out。

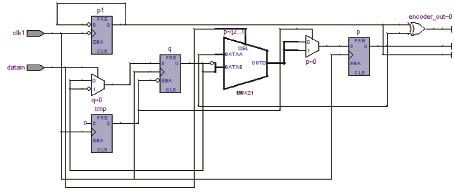

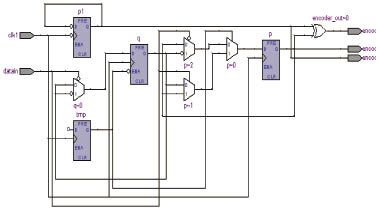

其具体VHDL模块图如图14所示。

图14 积分曼彻斯特码的模块图

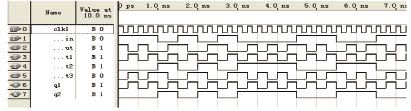

程序在QUARTUSII环境中编译仿真波形如图15所示。

图15 积分曼彻斯特码波形

双相-M码

双相-M码:除了相邻码元电平极性发生跳变外,当为“1”时中间发生跳变,当为“0”时中间不发生跳变,即时钟clk1为4分频,输入信号datain相邻码元极性跳变,遇“1”时在时钟clk1的上升、下降沿跳变,输出信号encoder-out。

具体VHDL模块图如图16所示。

图16 双相-M码的模块图

程序在QUARTUSII环境中编译仿真波形如图17所示。

图17 双相-M码波形

双相-L码

双相-L码,除了中间发生跳变外,当为“1”时相邻码元电平极性改变,“0”时相邻码元电极性不改变,即需要2分频时钟clk1,datain信号中间遇时钟clk1上升沿跳变外,且遇“1”相邻码元极性改变,“0”时不变,输出信号encoder-out。

具体VHDL模块图如图18所示。

图18 双相-L

程序在QUARTUSII环境中编译仿真波形如图19所示。

图19 双相-L码波形

双相-S码

双相-S码,除了相邻码元电平极性发生跳变外,当为“0”时中间发生跳变,当为“1”时中间不发生跳变,即与双相-L码相反,clk1为4分频。

具体VHDL模块图如图20所示。

图20 双相-S码的模块图码的模块图

程序在QUARTUSII环境中编译仿真波形如图21所示。

图21 双相-S码波形

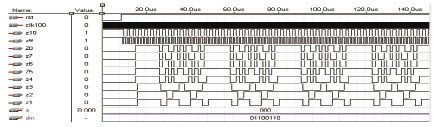

整体程序调试

整体程序在MAX-plusII环境中的编译仿真波形如图22所示。

图22 八种编码波形

总结

1) 运用VHDL编写以上八种编码是可行的。

2) 经过观察各模块的仿真波形,符合各个编码的特性。

3) 通过整体程序的调试仿真,并在FPGA上实现了波形的键选。

- 详解基于STM32的KEIL4 MDK软件仿真输出IO口的波形图(11-27)

- 单片机PWM程序及仿真波形图(11-26)

- Reed Solomon编解码器的可编程逻辑实现(06-21)

- 在FPGA上实现H.264/AVC 视频编码标准(07-23)

- WinCE下光电编码器的驱动程序设计(04-12)

- 一种基于DSP的张力、深度、速度测量系统(04-15)