基于并行流水线技术的RS255/RS233译码器设计

钱搜索模块接收KES模块的错误位置多项式信号δ(x),利用钱搜索算法逐个检查符号位是否发生错误,输出错误位置和错误位置多项式的奇数项之和,供EE模块计算错误图案和纠错。

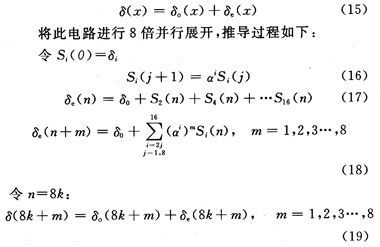

设错误位置多项式δ(x)可以表达为奇数项和偶数项之和:

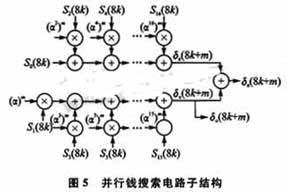

并行钱搜索电路子结构如图5所示。图中m表示并行模块编号数,m=1,2,…,8。所有的乘法器均是常数乘法器,8倍并行结构由图5所示的8个同样的结构组成。

EE(错误值计算)模块根据CS模块输出的δodd(x)以及KES模块输出的ω(x)计算出错误图案。

EE模块需要求解w(ai),电路结构推导过程和求解δ(ai)的过程一样,电路结构也基本相同,这里不再累述。

3 仿真验证与综合

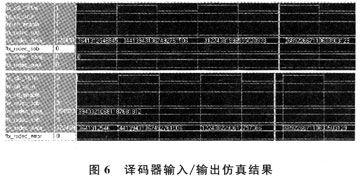

上述译码器采用自顶向下的设计流程划分模块,用Verilog HDL完成RTL代码的编写,然后在Mentor公司的ModelSim SE 6.1b仿真验证工具下编写测试代码进行仿真验证。仿真结果如图6所示,译码器能正确实现译码功能。

因本译码器可纠正16个错误,超过16个错误便不可纠正,在仿真时译码输入样本采用了2种:一种样本不超过16个错误,另一种样本超过16个错误。仿真结果表明,此译码器能在不超过16个错误的样本下正常译码。

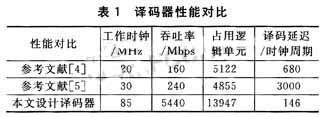

译码器在Quartus II 8.0上进行综合和优化,采用Altera公司Cyclone系列的EP2C15AF256C8芯片为目标器件。译码器的工作时钟频率可达85 MHz,数据吞吐率可达5 440 Mb/s,占用逻辑单元数为13 947个(片内共14 448,占用率为97%),RAM占用16 698位(片内共239 616位,占用率为7%)。译码器性能对比如表1所列。

与参考文献[4]相比,由于本译码器采用了并行结构在增加了不到3倍的硬件资源的情况下,吞吐率时钟比(吞吐率/时钟)提高了8倍,而且缩短了3/4的泽码延迟。与参考文献[5]相比,本文所采用的译码器增加了不到3倍的硬件资源,提高了8倍的吞吐率时钟比。由于参考文献[5]采用串行译码结构,本文所采用的并行流水译码结构较串行译码结构缩减了19/20的译码延迟。

- 利用FPGA实现外设通信接口之: 典型实例-字符LCD接口的设计与实现(06-05)

- 利用FPGA实现外设通信接口之: 典型实例-VGA接口的设计与实现(06-05)

- FPGA系统设计的仿真验证之: FPGA设计仿真验证的原理和方法(06-05)

- 一种基于Modelsim FLI接口的协同仿真技术(05-19)

- 流水线处理技术在数据集成中的应用(03-11)

- DSP设计中的流水线数据相关问题及解决办法(06-11)