基于FPGA的串行接口SPI的设计与实现

计的仿真、综合与实现

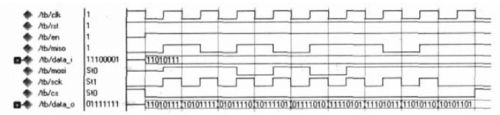

通过编写测试平台,并使用Mentor Graphics 公司的仿真工具ModelSim SE PLUS 6.1f 对该SPI 模块进行仿真,得到的仿真波形如图5 所示。

图5 SPI 模块的仿真波形

从图中可以看出,sck 的空闲电平IDLE=0,接收数据时刻是下降沿即ACTIVE-IDLE 边沿, 故该SPI 模块的工作模式是CPOL=0,CPHA=1,与设计一致。当en=0 时,cs=1,SPI 总线处于空闲状态。当en=1 时,在下降沿cs=0,sck 输出时钟信号,总线数据传输开始。同时,data_o=data_i, 移位寄存器存入待发送数据11010111.在第1 个周期上升沿,主机通过mosi 发送data_o 最高位1 至从机。在第1 个周期下降沿,data_o 左移一位,多出一个空闲位data_o[0],主机通过miso 接收从机发送的数据最高位1,并将其存入data_o[0],data_o=10101111.依此类推,后面7 个周期的数据传输过程与第1 个周期类似。8 位数据全部传输完成之后,cs=1,一个完整的SPI 总线传输过程结束。可以发现,data_o中的数据被一个一个从主机发送到从机,同时data_o 也被用来存储从机发送的数据。8 个周期完成之后,data_o 中存储的数据正是从机发送的数据10101101.综合以上分析,该SPI 模块的功能是正确的。

通过实验,在Xilinx ISE 9.1i 中完成了对该模块的综合与实现,并下载到Digilent 公司的FPGA 开发板Spartan-3E Starter 上进行验证,实验结果正确。综合工具使用ISE 自带的XST,下载工具使用ISE 自带的iMPACT.

4 结语

本文用Verilog 硬件描述语言设计了一个符合SPI 总线规范的SPI 主机模块,使用仿真工具ModelSim 对其进行仿真并给出了仿真波形。在Xilinx ISE 中对该模块进行综合与实现,并在FPGA 上完成了下载与验证。该SPI 主机模块的功能正确,工作稳定,可扩展性强。由于SPI 总线应用范围很广,利用FPGA 可重复配置的优点,该模块可以很方便地应用于各种场合。本文作者创新点:根据SPI 总线规范,用Verilog HDL 设计并实现了一个带有移位寄存器的SPI 总线模块,具有简洁高效、便于修改、可扩展性强等特点。

- dsPIC33F系列DSC的 SD存储卡接口设计(01-05)

- TMS320F240型DSP的SPI口的扩展 (02-20)

- 基于dsPIC30F2010的土壤水分测量仪的设计研究(08-27)

- 基于AD7862和dsPIC30F的数据采集系统(08-25)

- 基于DSPIC30F4011单片机的CAN总线通信设计(02-08)

- 采用SPI接口实现双DSP双向通信和同步(03-14)