基于VHDL的HDB3编码器设计

时间:06-05

来源:互联网

点击:

3 HDB3码编码在FPGA中实现的特性分析

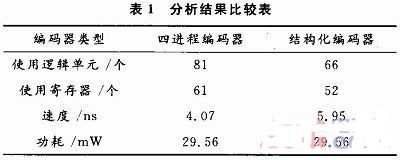

选用cycloneⅡ系列EP2C5T144C6器件,利用QuartusⅡ7.2对两种不同设计的HDB3编码器进行了分析。分析的主要内容包括:逻辑单元的占用、寄存器的占用、工作速度及功耗等的比较。仿真之后,主要选择了两组结果进行比较。分析结果如表1所示。从仿真结果可以看出,在结构化设计中,编码器总逻辑元件、专用寄存器使用与四进程设计相比各减少了18.5%,14.8%,表明结构化设计有利于减少器件资源的使用。

4 结语

根据实验和系统分析的结果,在FPGA中,利用VHDL语言设计HDB3编码器是可行的。尤其是结合VHDL语言程序设计的特点,利用不同的设计方式,可实现对HDB3编码器的优化设计。通过比较,在结构化设计中,编码器总逻辑元件、专用寄存器使用与四进程设计相比各减少了18.5%,14.8%。因此,结构化设计有利于减少器件资源的使用。

- DSP HPI口与PC104总线接口的FPGA设计(04-14)

- 基于FPGA的AD7862接口电路设计(01-01)

- 基于VHDL的感应加热电源数字移相触发器设计方案(03-20)

- 单板嵌入式硬件平台SingleBoard RIO(03-19)

- 设计嵌入式系统时选用NI LabVIEW的10大理由(03-19)

- 功能原型设计系列:为什么要进行快速原型(03-22)