基于CPLD的高效多串口中断方案

近几年来,随着后PC时代的来临,具有简洁、高效等特点的嵌入式系统得到了飞速的发展。嵌入式技术发展到今天已将各种计算机技术多层次、多方面的交叉融合在了一起。嵌入式系统加快了工业设计进程,降低了开发成本及其风险,使用简便,扩展灵活,高效精简,可方便地应用于各工业领域。 中断请求采用边沿触发来进行中断检测,通过将信号送到特定的引线来检测中断。每条引线对应一个可能的硬件中断,因为系统不能辨认哪个设备使用中断线,所以当多个1个的设备被设置成使用同一个特定中断时就产生了混乱。中断产生时,由专用的中断程序接管系统,首先把所有的CPU寄存器内容保存到堆栈里,并引导系统指向中断向量表。在中断程序执行后的一段时间中,中断控制软件把堆栈内容返回给寄存器,系统恢复中断发生之前 的状态。如此段时间中又有中断请求,将造成中断的设备判断混乱,从而会造成中断冲突、丢失,甚至使得设置无法正常工作。因此,每个中断通常被分配给单一的设备,使中断无法共享。 传统方法中,扩展多个串行口是利用多个中断源;但在嵌入式系统中,花费大量的中断源来扩展串口无疑是大量的资源浪费。针对这种情况,为了节省紧张的系统资源,本文提出一种实现高效多串口中断方案,可以利用单一的中断源来管理多个扩展串口,并保证多个串口中断的无漏检测与服务。

1 总体设计方案

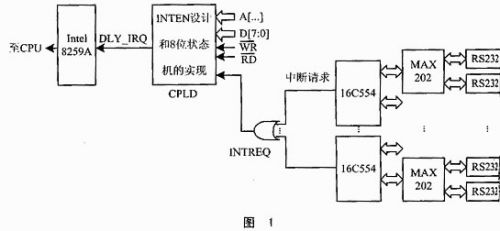

基本原理结构如图1所示。RS232串口通过驱动芯片MAX202转换成TTL电平,通过串口异步通信器件16C554输出中断请求,通过或门获得多个串口的中断请求INTREQ,再通过CPLD与中断控制器相连接。中断线INTREQ通过CPLD主要是在CPLD中做了一个1位的控制寄存器INTEN,用作中断允许控制位,并且根据16C554的中断请求INTREQ和INTEN的状态来最终生成DLY_IRQ,向CPU发出请求。CPU实时响应中断请求DLY_IRQ。在中断服务过程中,CPU按顺序逐个检查多个扩展的串口中断源,有中断请求的就给予服务。当刚刚检查过的中断又出现时,一方面靠CPLD中的一位寄存器INTREQ锁存;另一方面,当上一中断服务完毕时,CPLD中的8位状态机保证了一定时间的延迟。此延时中,中断控制把堆栈内容返回给CPU寄存器,恢复能获得响应。这样,即使在多个串口中断密集发生的环境下,扩展的多个串行口仍可获得实时性和可靠性较高的中断响应。

2 硬件实现

(1)MAX202 Maxim公司的MAX202芯片是标准的RS232电平转换器,是符合RS232通信标准的接口芯片;功耗低,集成度高,只用单一5V电源,每片有2个驱动器和2个接收器,具有2组接收和发送通道;全部接口电路简单,可靠性高,可实现TTL电平和RS232电平的直接转换。

(2)16C554 16C554是集成异步通信元件。在FIFO模式,传输和接收前数据缓冲为16字节数据包,减了CPU的中断数量。包含4个改良16C550异步传输器件,使得串行I/O更加可靠。每个信道实现串行和并行2种连接方式的转换;每个信道的状态可以通过CPU的操作读取,可以获取操作情况或任何的错误状态。三态输出为双向数据总线和控制总线提供TTL驱动能力、优先级中断系统控制、可编程的串行接口特性。

(3)8259A 8259A是可编程的中断控制芯片。每块芯片可管理8级向量中断, 具有8条中断请求输入线IRQ0~IRQ7,1条外中断请求输出线;具有4种主要工作方式,即全嵌套、循环优先级、特定屏蔽和程序查询方式;同时,还有4种从属工作方式,即结束中断、读状态、中断请求触发和数据缓冲方式。这些工作方式可以通过初始化命令字寄存器来实现。采用全嵌套方式时,芯片初始化后不必设置操作命令字。中断请求优先级是固定的:0级最高;7级最低。接受的8个中断请求信号为边沿触发。设定0级请求对应中断号为8,直至7级请求中断号为0FH。单片工作时,实际使用020H和021H两个端口。经过中断优先级分析器选中的当前请求的中断优先级。其相应的中断服务寄存器ISR位被置1,一直保持到中断服务程序在返回前发中断结束命令为止。在ISR置位期间,禁止同级或较低级的中断响应,开放较高级的中断请求。

(4)CPLD的编程 嵌入式系统都有灵活性的要求。因此,本系统选用了Lattice ispLSI系列产品,以适应不断扩展或开发新的产品以及1个硬件平台上多个品种的实现。使用可编程逻辑器件CPLD,有利于在系统设计和现场运行后对系统进行修改、调试、升级等。Lattice是带有在系统可编程(ISP)功能的可编程逻辑器件,即不需要重新修改PCB即可修改原有设计。

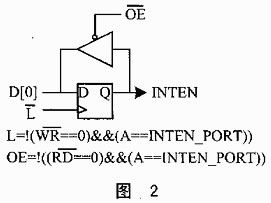

①在CPLD中设计1位寄存器INTEN原理图如图2所示。地址总线A对应INTEN的口地址,数据线D[0]对应INTEN的数据,数据在L的上升沿锁定。

②在CPLD中设计一个8位状态机。状态机由XCLK驱动,XCLK通过分频生成100kHz时钟,即Δt=10μs。

- 五、RS-232电平转换芯片及电路(12-12)

- ARM接口电平转换常用方法(11-11)

- 解析智能手机中的逻辑电平转换方案(08-13)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 基于DSP+CPLD的交流电机调速在水处理控制中的应用(11-27)