基于FPGA的数字音频广播系统信号调制系统的实现

引言

数字音频广播(Digital Audio Broadcasting,DAB)是广播通信系统由模拟向数字化演进的产物。在众多的数字音频系统方案中,Eureka 147 DAB系统是起源最早,也是技术发展最为完善的数字音频系统。本文所设计的DAB基带信号调制系统依据Eureka 147系统的技术要求。本文采用基于模型的系统没计方法,首先对DAB基带信号调制系统的各个模块进行算法层建模,之后利用Simulink平台以及Xilinx公司提供的可编程硬件模型库,将系统的算法层模型转换为可编程硬件模型,最后利用Xilinx公司的System Generator软件将经过验证的Simulink模型自动转换为FPGA可实现工程。

1 DAB信号调制系统简介

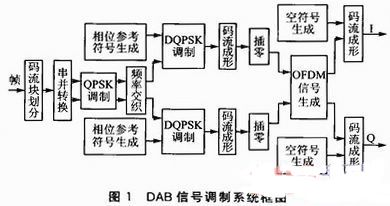

DAB系统基带信号处理链可以分为三个主要模块:第一个模块为信源编码系统,负责输入音频及数据源文件,并按照相关标准对不同的源文件进行信源编码,然后将编码后的数据流复用转换为特定的帧结构;第二个模块对经过信源编码的帧数据进行时域交织、信道编码等处理,然后将处理得到的数据复用转换为比特流;最后一个模块为信号调制系统,这部分系统将对输入的比特流进行正交相移键控调制、频域交织、差分调制、正交频分复用等一系列处理,并最终输出完整的DAB基带信号。图1给出了DAB信号调制系统框图。

2 DAB信号调制系统算法建模

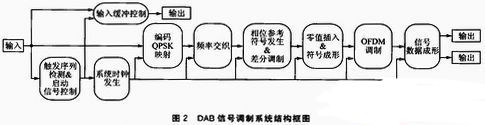

为了能够最终在FPGA芯片中实现DAB基带架构信号调制系统结,首先对整个系统进行算法层建模,DAB信号调制系统结构框图如图2所示。DAB信号调制系统的算法层模型具有以下主要模块:触发序列检测子系统、系统时钟发生子系统、编码QPSK映射系统、频率交织子系统、差分调制子系统、OFDM子系统等。需要说明的是,几乎每一个子系统(例如频率交织系统)都有自己的时钟域,并且系统时钟发生所提供的输出远比一个单一时钟信号复杂。

2.1 触发序列检测及系统时钟子系统

存DAB信号调制系统中,需要没计一个相应的序列检测系统来识别所接收到的数据流,当数据流中不包含触发序列时,DAB信号调制系统处于休眠状态,系统输出为零;当检测到触发序列时,序列检测系统将发出使能信号,使DAB信号调制系统对触发序列之后的数据流进行处理。

状态机是实现这个触发序列识别子系统的一个直观有效的方法。由于所要设计的DAB信号调制系统是一个复杂的实时信号处理系统,因此需要为系统建立全局时钟来规范处理时序。还需注意,系统的各个子系统之间的处理时序必须协调一致,否则输出端的DAB基带信号其物理层或逻辑层的帧结构会遭到破坏,全局时钟为各个子系统的协调工作提供了一个整体时序框架。同时,那些需要进行复杂处理的子系统(例如频率交织子系统、差分调制子系统等)可以以全局时钟为架构,建立自己的时钟域以及处理控制信号。全局时钟系统的建立主要依靠计数器及逻辑比较模块的组合使用。

2.2 编码QPSK映射子系统

假设DAB信号调制系统所接收到的比特码流中已经包含了块划分结构的信息,QPSK符号映射子系统将从接收到的编码数据流中将包含块划分的码元对还原,并对码流进行QPSK调制,即将还原的码元对映射为QPSK符号。这个子系统的算法较为直观,在还原码元对的处理中,涉及到的串并转换利用解时分复用算法实现,而QPSK符号的映射通过查找表实现。

2.3 频率交织子系统

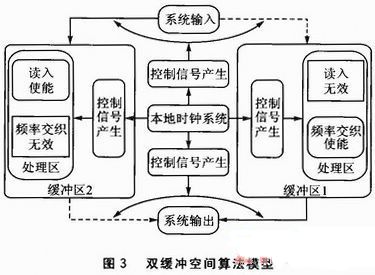

频率交织算法将改变QPSK符号与载波之间的对应顺序。实时处理要求大大增加了频率交织子系统的算法模型复杂度。为了实现对输入QPSK符号流的实时频率交织处理,本文设计了双缓冲空间算法模型,如图3所示。

双缓冲空间算法模型核心思想是提供两个并行的缓冲空间。在同一OFDM符号周期(384个QPSK符号周期),一个缓冲空间接收QPSK码流,而另一个缓冲空间处于读入锁定状态,并进行静态频率交织处理。此时系统的输入端连接至前一个缓冲空间,而系统的输出则由第二个缓冲空间提供。在一个OFDM符号周期结束后,两个缓冲空间的工作状态对调,之前接收QPSK码流的缓冲空间处于读入锁定状态,进行静态频率交织处理并提供系统输出;而之前进行频率交织的缓冲空间则处于读入状态,并从系统的输入端接收串行的QPSK码流。

2.4 差分调制子系统

经过频率交织子系统的处理,经过QPSK涮制的符号流,其在一个OFDM符号周期内的载波对应关系发生了改变,从而使频域的信息流得到了一定程度的无序化,提高了信号抗衰落的能力。但是,由于调制方式为QPSK,信息被调制在载波的绝对相位上,这就要求接收端的参考基准相位具有很高的稳定性,否则可能会发生由于参考基准相位的不稳定而导致码信息的误译情况。为了进一步增强系统的可靠性,DAB基带信号处理过程中引入了差分调制,将QPSK符号流转换为DQPSK符号流,从而将信息调制在载波的相对相位信息上,提高了系统的稳定性。

在差分调制系统算法模型中,需要一个本地存储区存储频率参考符号,每一帧信号的差分调制处理流程如下。存帧头空符号输入的时候,系统不做任何处理,直接输出空信号。在频率参考符号周期内,系统的输入端依旧是空信号,但是本地存储区将会在系统的输出端提供频率参考符号,同时将频率参考符号引入反馈缓冲区。当第一个FIC符号输入的时候,反馈缓冲区的频率参考符号会与之同步,对应的QPSK符号做模8相加,相应的子载波进行了差分调制,同时输出端经过模8相加的编码DQPSK符号被引入反馈缓冲区。当第二个FIC符号输入的时候,以反馈缓冲区中经过差分调制的前一个OFDM符号为基准进行模8相加,当一帧信号的所有OFDM符号都经过处理后,反馈缓冲区将被清零,为相位参考符号的冉次装载做准备。图4描述了差分调制系统的算法模型。

经过差分调制得到的DQPSK符号流将通过零值插入子系统、OFDM子系统和数据成形子系统的处理。零值插入子系统的算法模型与双缓冲区算法模型类似,OFDM子系统的核心算法为快速傅里叶逆变换,数据成形子系统将会渊整经过处理得到的OFDM符号的数据格式并向输出端提供最终的DAB基带信号数据流。

- 基于SIMULINK的心电信号源系统设计分析(11-24)

- 使用基于模型的设计进行早期验证和确认(01-25)

- 基于DSPBuilder的FIR滤波器的系统设计(03-19)

- 基于FPGA设计DSP的实践与改进设计(05-11)

- SPWM波控制单相逆变器双闭环PID调节器的Simulink建模与仿真(09-22)

- G.726语音编解码在SoPC系统中(06-06)