基于FPGA实现视频图像的一种运动估计设计

时间:06-05

来源:互联网

点击:

3 实验结果与分析

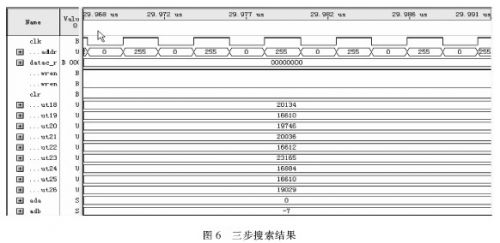

本设计采用Stratix II系列的EP2S15F484C3器件进行仿真,仿真结果如图6所示。

由仿真结果可知整个搜索过程完全符合时序要求,总的逻辑资源占用率是27%。组合查找表使用了2 169个,占总数量12 480的17%。专用逻辑寄存器使用了2 855个,占总数量12 480的23%。而用的总的寄存器数也就是2 855。使用了180个片上引脚,占总个数的52%。使用了86 088比特的块存储器单元,占总的快存储器数量的21%。搜索到的最佳运动矢量(0,-7),由前两步的搜索结果可知其完全正确。

4 结束语

本文中采用FPGA设计的运动估计方案无论在搜索速度,资源利用还是时序控制上都具有一定的优越性,可以大大提高视频编码器设计的性价比。另外,随着半导体工艺的不断进步,FPGA的性价比将不断提高,将使得运动估计乃至视频编码的技术不断提高。

- 用数字信号处理器优化视频编码器(03-11)

- 基于ADSP-BF561的H.264视频编码器的实现(01-10)

- 基于ADSP-BF561处理器的视频编码器平台(01-16)

- 基于嵌入式平台的视频编码器的实现(07-30)

- 基于ADSP-BF561的H.264视频编码器系统的实现(03-05)

- 数字图像倍焦系统设计与实现综合实例之:设计需求分析与芯片选型(06-05)