芯片设计中的可测试设计技术

模拟挑战

当涉及模拟电路时,一切都不一样了。“我们将模拟部分与数字电路分割开来进行调试”Lee 解释道。“对两者的调试技术是不一样的。在模拟领域,要打开环回途径,可能要将所有的调试拿到封装脚之外进行。由于在模拟电路中活动基元并不与时钟同步,因而无法对其进行捕捉。”

模拟电路与数字电路类似,随着几何尺寸的缩小,设计师已经看到了探测和实验设计的能力,Analog Devices的Paul Ferguson 认为。“我们习惯了将激光切割器用于探测台来修改电路。后来,随着几何尺寸的减小,我们转移到了聚焦离子束系统。对于250 nm 或更大的间距非常实用。这表明,实际上说,如果采用65nm 工艺,只能改动上面的两个金属层。”

这种情况引发了模拟设计风格的一个有趣的变化, Ferguson说。“最近我们在做一项90nm 设计的PLL,我们发现必须首先完成VCO(压控制振荡器),才能建立合适的模型。所以,我们引入了一些线路,将增益和其它参数调整到所能达到的上部金属层。这对于调试过程的确很有益处。”

Matt Ball 是单芯片无线电厂商Jennic公司的混合信号项目工程师,他也强调要将关键模拟信号置于可取位置的重要性。“我们加入了尽量多的可编程性和数字调整功能,”他说。“有些东西必须为金属微调的, 我们将那些位置变成单一的掩模层级别实现可访问性。”

除了将实时信号引到上部金属层或封装脚上,今天的模拟设计师还有其它武器设定及观察电路的状态。最重要的是在微细几何尺寸上进行,模拟电路与校准和监测它们的数字电路间要有密切的协作。

CSR的McCall 说在其设计中,ADC监测器可确定模拟电路中数字监视电路的多个点。这些点通过将转换器的输出接到封装的外部,为调试工程师提供了访问模拟部分行为的机会。“通常重要的模拟信号在某些点进行数字化处理了”Ball说。“为什么不进行采样,以片上DSP进行滤波,输出我们能够看到它的结果呢?”

设计滤波器或放大器以便数字电路能够调节所有重要电气特性,这似乎有些大动干戈了。但是在首次工作的芯片和在调试前有两层新金属掩模层的芯片之间产生的不同甚至可以启动设计的数字部分。而且,在小于90nm的工艺中,设计师必须面对越来越强的可变性,这些由数字调整就成了必须,这样才能生产足够数量的有用芯片。

如何进行调整?对于无线电芯片上信号的精度和频率,IF (中频)信号,在测试模式中可以只用布线和模拟多路复用将信号引出封装之外。“在中频部分,缓冲器非常有用。”Ball 说。“从重要的节点取得信号送到针脚,就可以看到需要看的结果。”Analog Devices的Ferguson也同意此观点。“就调试而言,往往不需要比模拟多路复用器所能提供的精确度高多少,就可以看到振荡或20% 的增益误差。”

如果不能将信号引到封装之外,有时可以将 信号路由到片上数据转换 器。“芯片上通常有一个附属ADC监测芯片温度,电池电压等等,”Ferguson 解释说。“在调试中我们将庞大的多路复用器置于其前面,用来检查模拟部分的其它节点。但要小心:额外的测量电路会损坏其它部分。例如,接通多路复用器观察节点,会提高稳定电路的振荡能力。如果调试信号无意中跨过电源域,可以引入没有遇到过的寄生电流路径。”

Ball 也同意这种警告,必须选择适当的方法,他说:“缓冲模拟信号时所产生的10fF或20fF可改变节点的行为。” Jennic倾向于只根据以前出现问题的区域,如带隙电池,构建其调试方案。“我们更喜欢添加旁通电路,以防出现问题。”Ball补充说。这种保守思想可降低故障电路的出现机会。

经过计划,加上运气,以及一点雅致,可以重新利用功能模块进行调试。许多模拟信号在数据转换器中终止,所以至少其中部分是可观察的。Ferguson 指出,可以轻松地开关s-Δ转换器作为滤波器工作,以对进入的模拟信号进行观察。或者小心地将位流路由到针脚,在转换器两侧都可观察。一旦对数据进行数字化处理,就可以使用CPU 或DSP 模块调节及压缩或测试对其的断言。

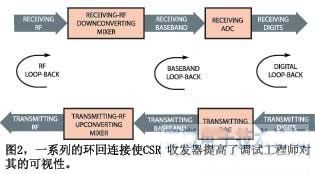

也可以将调试智能(相当于简单的网络分析仪)构建到一个模块中。环回路径可使用发射器和接收器来互相检查(图 2),有些电路可以抽取结果的模拟波形。“在我们千兆位PHY (物理层)设计中,我们在PHY 块中捕捉到了一些模拟信号,”Broadcom Hublitz 介绍说。

发展前景

不难想象,在系统设计早期阶段,每个功能模块接受足够的自检能力在全速运行期间进行自身诊断,并在DFT扫描链可处理的级别上实现这种能力。这种方法通常需要输入缓冲器或信号发生器对模块仿真,还要有输出捕捉寄存器或ADC 对其观察,以及足够的内部断点和跟踪能力揭示模块的内部工作情况。一些SOC 设计团队现在正在进行此项计划。这样实际的实现就成了架构师认为必要的调试支持级别与设计所能承受的费用间的折中。

进一步拓展此概念,完美系统的设计师可以利用重定某些功能模块目标,作为信号源或其它模块的捕捉设备。附属的ADC 是个很好的例子,这样的机会还有更多。例如,增加快速数据转换器可以将信号处理模块变成网络分析仪或数字示波器。对控制逻辑稍作添加,即可将缓冲器 SRAM 阵列转换为跟踪缓冲器。

按这种思考方式,片上的功能模块可成为大量的调试资源,只重置几个多路复用器和模式开关即可。但此过程需要深谋远虑。这样组织会影响平面规划和全局布线。必须在设计开始时进行,而不能在最后的实现时进行。

Ferguson 认为,某些工具也可支持这种过程。精密的工具可自动安装这种结构,如扫描链、扫描控制器及矢量发生器等。而且,DFT 硬件在寄存器级别的诊断上是必不可少的。但是,并没有支持创建调试结构的工具。Ferguson至少想要看到一种将混合信号模块视为具有能观性和能控性,并能扫描检查简单错误的检测工具。理想状态下一种工具应该能够贯穿于一项设计,并能提出一种调试架构和工艺。但这是以后要解决的问题。

- PLC及特殊功能模块在玻璃熔窑自控中的应用(12-14)

- 单片机常用功能模块的使用 Part4. 定时器(11-17)

- 单片机常用功能模块的使用 Part5. 独立按键(11-17)

- 单片机常用功能模块的使用 Part2. 共阴共阳数码管(11-17)

- 单片机常用功能模块的使用 Part6. 中断(11-17)

- 单片机常用功能模块的使用 Part3. 多位共阴共阳数码管(11-17)