硬件描述语言Verilog HDL设计进阶之: 典型实例-状态机应用

时间:06-05

来源:互联网

点击:

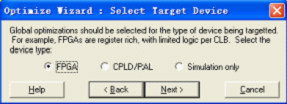

实例中选择FPGA,如图4.15所示。

图4.15选择目标器件

②选择状态机的优化方向,用户可以选择速度优先、占用面积优先以及手动设置。在本实例中我们选择速度优先,如图4.16所示。

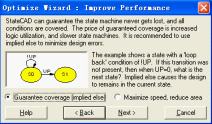

③对状态机的性能改善方式进行选择,如图4.17所示,本实例选择保证覆盖面积模式。

图4.16状态机优化方向

图4.17状态机性能改善模式

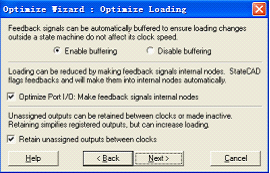

④加载优化参数设置,如图4.18所示。

图4.18加载优化参数设置

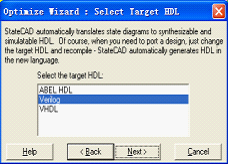

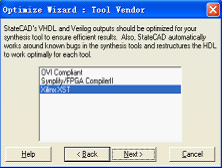

⑤为状态机选择输出的HDL语言形式以及综合的EDA工具。在本实例中,选择Verilog语言及XilinxXST综合工具,如图4.19所示。

图4.19选择目标HDL语言和EDA工具

经过这5个步骤的设置,就完成了状态机的优化设置,可以开始生成Verilog语言形式的状态机了。

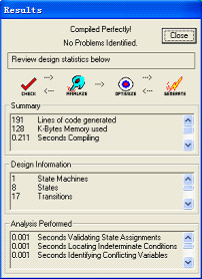

选择StateCAD工具栏上的 按钮,开始生成Verilog状态机。如果设计没有错误,将出现如图4.20所示的结果对话框。

按钮,开始生成Verilog状态机。如果设计没有错误,将出现如图4.20所示的结果对话框。

图4.20状态机生成结果

单击“Close”按钮后,就可以看见生成的与状态机名称相同、后缀为.v的源文件了。

2.添加设计输入

将使用StateCAD生成的状态机源文件加入工程中,即可查看并编辑相关的状态机的代码了。

3.设置器件及管脚约束

按照开发板的说明进行相关的设置。

4.下载验证

本实例的状态机在开发板上下载后,将能看到开发板上的8个LED循环变亮,即实现跑马灯的功能。

4.6.3参考设计

本实例相关参考设计文件在本书实例代码的“典型实例6”文件夹。

VerilogHDL 状态机 FPGA 相关文章:

- Verilog门电平模型化(06-06)

- VHDL:中文版Verilog HDL简明教程:第3章 Verilog语言要素(06-06)

- VHDL:中文版Verilog HDL简明教程:第2章 HDL指南(06-06)

- VHDL:中文版Verilog HDL简明教程:第1章 简介(06-06)

- VHDL:中文版Verilog HDL简明教程:第3章 Verilog语言要素(续)(06-06)

- 基于Verilog应用(06-06)