基于高性能DDS芯片AD9959的超宽带步进频率探地雷达设计

0 引 言

探地雷达是近10年迅速发展起来的一种无损探测新技术,它具有探测速度快、高空间分辨率、对目标的三维电磁特征敏感、可实现连续透视扫描以及二维彩色图像实时显示等优点,目前已在工程勘察、水利隐患探测、工程质量检测、地下管网探测以及考古等领域得到了广泛应用。

随着雷达技术的迅速发展,人们对雷达信号的要求也越来越高。高精度、高扫描率、高抗干扰性、低截获率成为人们追求的目标。满足这种需求除了靠产生复杂的雷达波形外,还需要在雷达系统中应用高性能的器件。

直接数字频率合成方法具有传统方法所不具备的许多突出的优点:高频率分辨率、高频率切换速度、频率切换时相位保持连续、超宽的频率范围、能实现各种调制波和任意波形的产生以及易于实现全数字化的设计等。AD9959是一款高性能DDS(直接数字频率合成器)芯片,可方便快速地产生线性调频、单频脉冲及步进频率信号,其工作频率高达500 MHz,杂散性能指标更高于以前的产品。

1系统组成及工作原理

1.1探地雷达探测原理

GPR(探地雷达)是利用高频电磁波(1 MHz~1 000 MHz)以脉冲的形式发射电磁波,雷达波在地下介质中传播时,遇到存在电性差异的地下介质或目标体时,电磁波便发生反射,根据接收天线接收到回波的波形、强度、电性及几何形态进行处理、分析,从而达到对地下目标体的探测,如图1所示。目前使用较多的是无载频脉冲体制(Impulse)、FMCW(调频连续波)及SFCW(步进频率连续波)体制。

典型的步进频率探地雷达发送N个相参脉冲,其脉间频率通常以一个固定的频率增量△f递增,如图2所示。

一个脉冲帧中第n个脉冲的信号频率可以表示为:

式中:f0为射频,也是起始频率;τ为每个脉冲的脉宽,T为脉间间隔,可根据模糊距离调整。

N个脉冲组成一脉冲帧。帧时间即发射N个脉冲的时间,又称为CPI(相关处理间隔)。这种信号的有效带宽为Beff≡N△f,由于通常要求△f≤1/τ,因此,提高信号有效带宽可以通过加大N。相应的信号是Acos 2π(f0+n△f)t。假设信号在均匀介质中传播的速度为v,一个距离R的点目标回波可表示为WR

式(4)符号后第1项是常相移项,没有意义,第2项是频率变化率△f/T和双程时差的乘积。这样距离转换成频移,因此,可以通过频率分辨达到分辨和测量距离的目的。由于距离的测量是由DFT(离散傅里叶变换)完成,距离分辨力△R和无模糊距离Ru分别依赖于DFT的频率分辨率和最大无模糊频率测量。这就是步进频率连续波体制雷达的工作原理。

1.2系统总体方案设计

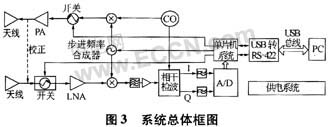

系统采用外差式结构,设计系统总体框图如图3所示。

CO(相干振荡器)是一个10.7 MHz的点频源。步进频率合成器AD9959产生频率范围在20 MHz~140 MHz的步进本振信号,与CO混频后,产生射频信号,经PA(功率放大器)放大,通过天线发射出去。接收到的回波信号经LNA(低噪声放大器)放大,与步进本振混频,得到IF(中频信号)。IF信号经带通滤波和放大后,与CO进行相干检波,得到I、Q信号。I、Q信号分别经滤波后,送入A/D转换器进行数据采集,所采集的数据经USB接口送给PC进行数据处理工作。在雷达系统中,由单片机和CPLD(复杂可编程逻辑控制器)完成系统的控制和产生各种时序。

为了校正系统在各个频点的相位初值,系统要进行校正。用同轴电缆和衰减器将系统的发射和接收端口连接起来,可以进行系统的校正工作。 2 AD9959工作原理、特性和应用

2.1 AD9959的工作原理和特性

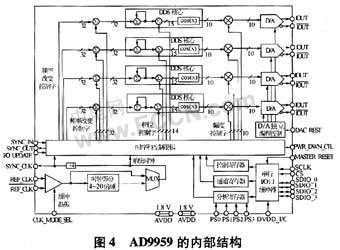

高性能DDS芯片AD9959是美国AD公司采用先进的DDS技术生产的4通道、10位D/A转换器、最高时钟为500 MHz的高集成度频率合成器,可方便快速地产生线性调频、单频脉冲及步进频率信号。AD9959允许对4个内部同步输出通道独立编程,能够对多通道信号之间的不平衡提供有效的校正控制,通过一个公用参考时钟内部同步其独立的通道,每通道功耗小于165 mW。可编程的通道控制可以对由于模拟处理(例如滤波、放大)或者PCB(印制电路板)布线的失配而产生的外部信号通道的不均衡进行校正。如果需要增加通道,AD9959允许通过菊花链方式连接附加的DDS芯片。每个通道都含有一个高速10位D/A转换器,每一个完全可独立编程的通道都提供14位的相位偏移控制、32位频率分辨率控制和10位幅度控制。器件还支持直接和线性扫描调制,同时可以达到大于65 dB的通道隔离度。集成的32位频率控制字在采样时钟为500 MSPS(百次采样每秒)时能够使每个通道的分辨率设置到116 MHz或小于116 MHz。

AD9959的内部结构如图4所示。

AD9959还有以下特性:内置500MSPS时钟下4通道DDS;增强性数据吞吐串行I/O口;双重电源供给系统(DDS核心为1.8 V,串行I/O口为3.3 V);可实现多片同步;可利用PLL(锁相环)4倍~20倍倍频等。

- 基于Virtex5高性能FPGA的脉冲激光测距系统设计(01-02)

- 三种测风设备测量精度的对比分析(03-26)

- 用于雷达测试和验证的自动化测试设备(05-15)

- 用于系统级测试和PCB配置的高级拓扑结构(05-16)

- 使用LabVIEW重写电子战争模拟程序(06-14)

- 基于虚拟仪器的雷达信号模拟系统(10-23)