一种可以提高DFT设计测试覆盖率的有效方法

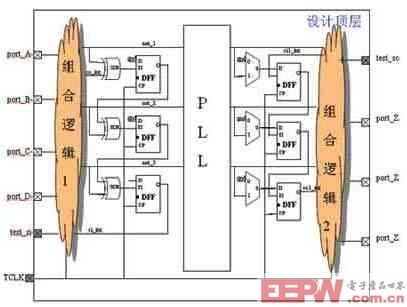

针对图2所示的数字-模拟接口,部分模拟模块输入信号通过组合逻辑给出,但在测试时并没有逻辑将这些“终点”的信号影响引出观察,因此这些点是不可观测的。这与DFT设计可观测要求(需管脚直接输出)不相符,可能造成测试覆盖率的损害。同时,部分模拟模块输出信号控制相应的组合逻辑,但在测试中,这些点是“浮空”(不可控制)的。这与DFT设计可控要求(需管脚直接输入)不相符,造成测试覆盖率的降低。图4给出了类似前者的定制解决方案,其实质也是把这些不可控和不可测点连到测试链上去,让这些逻辑间接可观测或可控制以改善测试结果。

图4添加控制点和观测点提高测试覆盖率(数字-模拟接口情况)

如图所示,在模拟模块输入信号处添加少量异或门和选择器件,并将它们连到扫描链上去。当控制选择信号为“0”时,电路处于正常工作状态,模拟模块的输入管脚正常接收功能信号。当选择控制为“1”时,电路处于测试状态,用异或门或者其他器件将未能观测管脚的变化引出,相当于这些管脚间接可以被观测了。

如图所示,在模拟模块输出信号处添加一个带有选择端的寄存器。当控制选择信号为“0”时,电路处于正常工作状态,模拟模块信号正常输出到后续的功能逻辑。当选择控制为“1”时,电路处于测试状态:在移位过程中,这些点由测试链预置相应的值;在捕获过程中,将之接地防止不定态在设计中的传播。

对于其他的模拟模块如ADC, 存储器等,采用类似的方法可改善整个芯片的测试覆盖率和测试效率,达到目标测试效果。

结语

在前面提及的实际项目DFT设计中,功能逻辑部分含有万余寄存器。为提高测试覆盖率,添加仅12个寄存器及很少部分组合逻辑作为测试点后,即可将测试覆盖率从原来的95%提高到 98.3%。由此看来,这种方法是很有效率的。并且可根据项目实际需要,添加更多点以期达到更高覆盖率,理论上测试覆盖率可接近100%。

推荐RTL功能设计时就能考虑这种测试结构。这样做设计工程师之间能够了解彼此的设计需求,功能测试结构明晰,在DFT设计过程中省去很多麻烦。如果发现这类问题在RTL完成之后,一些DFT工具也提供用户自定义的测试点插入,但是要注意测试控制信号选取一定要与需要的测试模式匹配,否则无法完成相应的测试期望。这种方法的关键是了解在哪里加测试点更为有效。

无线RF 通信测试 示波器 高速串行 嵌入式 测试测量 相关文章:

- 汽车电子中的无线RF信号测试方案 (01-12)

- 采用LUYOR-2120B紫外线灯检测食品包装的荧光性(12-05)

- 使用数字万用表判断三极管管脚(图解教程)(09-07)

- 抗干扰电路在测控装备中的设计与实现(06-27)

- 泰克示波器的使用方法(05-14)

- 滤波器MAX274在电力参数测量中的应用(09-29)