使用FPGA测试的一些有效方法

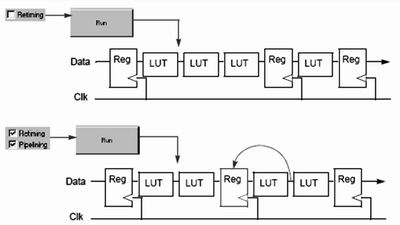

中的时钟频率。 在综合中采取的第二个方法是使用综合工具提供的pipeline和retiming功能。这些功能可以调整寄存器的位置,使之在不改变逻辑的前提下,将寄存器的位置调整的更加合理,如图2所示。这个功能主要用于组合逻辑过长且不合理的情况下。当然,如果某些乘法器位数过宽而结果没有寄存的时候也会导致组合逻辑时序紧张。当发生这种情况而retiming功能又无法纠正时,就需要设计者在做设计的时候对乘法器的输出结果做一拍寄存,同时其余的控制逻辑也要做相应的调整。 图 1 DSP48示意图 布局布线阶段解决时序问题 当综合工作完成,进入布局布线的阶段后,仍然有两种方法可以改善逻辑时序问题。 第一种是手动增加并调整BUFG(Global Clock Buffer)。BUFG是Xilinx的全局时钟资源,所有时钟树的起点都是BUFG,位于FPGA的北极和南极。当布线后仍有负的slack时,有可能是某些当作时钟使用的信号没有被放上时钟树,此时就要手动将这些信号放上BUFG。若遇到门控时钟,还应该使用BUFGMUX资源。另外,在Virtex-4中,北部的BUFG主要负责北部的时钟,南部的BUFG负责南部的时钟。在我们的项目中,共有十余个时钟,因此,BUFG位置的选择也很关键。有些时候,工具不能解决一切问题,只有手动调整BUFG的位置,或将BUFG的位置信息写入用户约束文件才可以取得较满意的效果。 在Virtex-4中共有16个BUFG,若都被使用且经手动优化后仍不满足要求,那么还可以使用ISE提供的Floorplanner工具,对设计的各个模块手动进行位置摆放,使各个模块尽量靠近自己所使用的时钟树。 代码一致性 对于经过FPGA验证的代码而言,最担心的是经过验证的代码和进行流片的代码不一致。导致这个现象产生的原因是多种的,其中版本控制和由于FPGA、ASIC专用器件不一致而引起的问题是最常见的两个问题。 对于经过FPGA验证的代码,为了能够使被测代码可以顺利的在FPGA进行验证,一般都采取了FPGA专用的器件。这些FPGA专用器件在ASIC中是不存在的。为了解决这个问题,我们通常采取“假代码”(Fake Code)解决。 顾名思义,“假代码”就是在代码中保留FPGA专用器件的名称和接口,但是在FPGA和ASIC中使用不同的器件内核。该器件若在FPGA下使用则使用FPGA专用器件,若在ASIC下使用,则使用自己编写的代码。尽管这种做法仍然无法保证代码的完全一致,但是却最大限度的避免了代码的差别。 结语 究竟使用EDA 仿真工具还是使用FPGA进行流片前的功能验证一直是业内讨论的热点话题,不同的设计、测试人员也有自己的观点。本文针对使用FPGA进行验证测试所遇到的一些问题提出了相应的解决方法。■

Synplicity Synplify 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)