MIL-STD-1553A/B数据总线自动测试仪的设计

激励正弦波,并通过示波器模块来采样响应信号,并根据激励信号和响应信号的真有效值来计算受测设备的输入阻抗。

过零点稳定度用来测试曼彻斯特解码器的解码能力和终端设备时钟的稳定度的。如果设备的时钟不稳定,即使解码器的解码能力非常好,也会造成接收误码。

标准规定的接收信号幅值为0.28~27V之间。当总线信号的幅值在此范围之内时,设备的解码器须对总线数据正确解码。

如果总线设备的输入阻抗过低,往往会加大总线的负荷,从而降低总线信号的幅值,缩短其它总线设备的寿命。

共模抑制能力是用来考察总线终端设备隔离变压器的隔离度的。在正常情况下,变压器次级线圈上的共模噪声是不会影响初级线圈上的差分信号,否则共模噪声将会在初级线圈接收的差分信号上叠加一个干扰,从而影响终端设备的信号接收。

AT15000对电气特性的测量采用全自动方式,其内置的示波器模块会自动捕获需要测量的总线信号,并计算出相应的特性参数。在测试过程中无需人工干预,用户只需在其测试脚本中加入需要测试的项目即可。针对BC和RT的测试,在每个测试项目完成后,AT15000会自动将测试结果写到测试报告中,为测试提供了极大方便。

2. 协议测试

标准规定的协议测试分为常规测试和故障注入两个部分,常规测试要求BC/RT能接收/发送MIL-STD-1553B总线规定的命令,要求BM能够正确解析总线协议,故障注入要求测试仪能够在总线上注入标准规定的各种故障。在进行协议测试的时候,首先要完成常规的协议测试,否则故障注入测试无法完成。

为了满足测试标准的要求,一个总线测试ATE除了要具备仿真器、信号发生器、总线仿真终端的功能外,还需要具备MIL-HDBK-1553规定的以下功能:

能够注入最大不小于250ns的过零点偏差;

能够在任意总线字上注入奇偶校验错误;

能够在不同的消息上注入任意消息长度错误;

能够在任意总线字上注入任意长度的字长错误;

能够在总线字的任意位上注入相位编码错误,并且可以在错误位上输出高电平或者低电平;

能够在总线上注入数据连续错误;

能够在总线上注入替换命令;

RT的应答时间在0微秒到14微秒之间可调;

RT可以采用任意地址来应答总线命令;

可以通过软件关掉RT的应答(数据要能正常接收);

可以在任意总线字上注入标准规定的5种同步头错误;

能够产生总线切换命令;

能够正确识别协议规定的所有模式命令;

能够在总线上注入均方根为140mv(直接耦合方式200mv),频率范围为1K~4Mhz之间的高斯白噪声。

如果采用市面上通用的MIL-STD-1553总线控制芯片,无法实现上述的总线故障注入功能,同时也没有商用的带有故障注入功能的总线控制芯片出售。所以为了能够实现上述功能,测试设备开发商需自行开发带有故障注入功能的1553总线控制芯片。

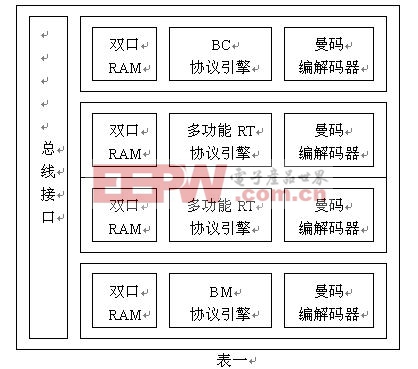

基于上述考虑,矽微公司自行开发了总线测试设备专用的1553总线控制IP核,可以在ACTEL和ALTERA的多个系列的FPGA实现。用于采用硬逻辑的方式来注入故障,所以改IP核能够实现标准所规定的全部故障注入功能。此IP核的功能框图如表一:

如表一所示,控制器IP核中实现了一个BC、一个BM和两个多功能RT,这些功能可以同时工作,并且可以同时仿真32个RT。IP核采用64M时钟,可以以15.6ns的分辨率在总线上注入过零点偏差,大大提高了总线测试的精度。经过矽微公司数个型号的总线测试设备的验证,证明这个IP核的设计是合理的,工作状态是稳定可靠的。

如果只实现1553控制器的IP核,还是无法实现总线的自动测试的。除总线控制器外,还需实现示波器的采样逻辑,信号发生器的逻辑以及时域反射计的逻辑。同时还要根据总线测试标准的要求,将这些逻辑组合起来,以方便总线电气性能的测试。AT15000采用ALTERA公司的CYCLONEIII FPGA芯片,在FPGA中实现了上述几种逻辑。其中的示波器逻辑可以由1553控制器的逻辑来触发,使得总线电气特性的测试变得非常简单。

作为ATE,总线测试设备需要具备较高的自动化程度,尽量减少人工干预。所以在设计测试仪软件的时候,需要仔细分析测试标准,将测试项目分类并细化成若干个子测试项目,让用户可以自由选择测试项目并定义测试顺序,以使测试更加灵活,进而满足不同测试场合的需要。AT15000根据总线终端设备类型将测试分为RT测试、BM测试和BC测试三种,同时将每种测试分为很多个子测试项目,用户可以通过脚本的形式来自由选择测试项目和定义测试顺序。在三种类型的测试中,除了RT的测试之外,BM和BC的测试需要受测设备的软件配合,所以在测试BM和BC的时候,用户需要编写受测设备的软件,用以配合测试仪的测试。

由于BM只具

- 1553B电缆网络测试方法研究(06-22)

- 1553总线测试仿真系统设计与实现(07-30)

- 通用1553B总线的信息监控系统的设计(04-06)

- 源同步信号跨时钟域采集的两种方法(04-07)

- 面向信号自动测试系统信号组件的设计(04-17)