多并行处理器接收机设计与实现

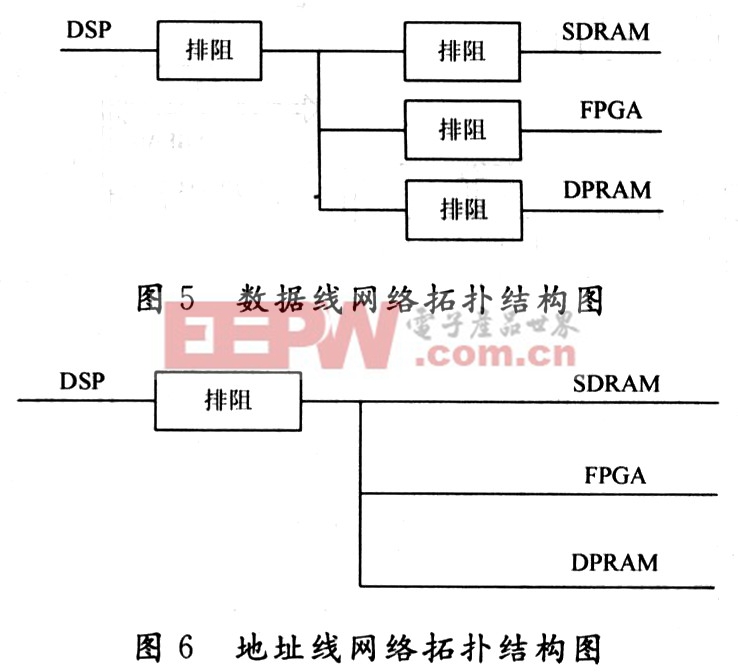

两个C6416T通过串口1和串口2相互连接,可实现全双工通讯,同步串口的最高时钟速率可达l/4CPU时钟频率。 4 接收机板的SI仿真 从图5,图6中可以看出,地址线的网络拓扑结构在DSP的外设端未加匹配电阻,这样做的目的是为了减少PCB布线的繁琐性,但为了减少接收端反射信号对DSP端驱动信号的影响,这样做的前提首先应当保证符合信号完整性的要求。该设计中由于元器件布局的原因,DSP的地址线到其每个外设的距离相差不大,这样只需要在靠近DSP端加上匹配电阻就能符合SI的要求。当然,在DSP及其外设每端都加上匹配电阻的话,信号质量会更好,DSP数据线就采取了这种做法,由于它的数据线与其每个外设的距离不同,要保证信号完整性就不得不在靠近各器件这端的中部都加上匹配电阻。 图7,图8中,U6为DSP,它作为驱动源,输出100 MHz的矩形波信号驱动它的外设;U7,U8为SDRAM,U10为DPRAM,U13为FPGA,它们作为DSP的外设,接收DSP发送来的信号。从这两幅图中可以看出,反射信号对数据线和地址线都有一定的影响,但都满足信号完整性的要求,同时也验证了在两种不同拓扑结构下所产生的信号质量不同。 5 测试结果 6 结 语

(2)3C120模块中两片FPGA(3C120A和3C120B)之间的通讯

它们也有两种通讯方式:DPRAM通讯、自定义I/O通讯。两片3C120通过DPRAM通讯的原理与两片C6416T相同。另外,两片3C120之间还互连了一些I/O口,在实际应用当中可以对这些I/O口进行定义,让其来完成两片3C120间的数据交换。

(3)3C120模块与C6416T模块之间的通讯它们包括两部分,两片3C120分别与所对应平行的C6416T之间的通讯。每片3C120与所对应的C6416T之间可通过EMIFA总线、SPI和中断来进行数据的交换和控制。

信号完整性(Signal Integrity,SI)是指在信号线上的信号质量。在高速电路中来自接收端的反射信号很容易到达驱动端,如果反射信号很强,叠加的波形就有可能改变原来的逻辑状态,导致电路无法正常工作。该接收机板总线传输速率要求很高,所以在PCB布线之前,应预先进行调研,以形成规则或设计准则,从而确保设计结果不出现明显的信号完整性问题,这是SI仿真的前仿真。前仿真的过程是,首先将主要器件的IBIS仿真模型加到待布线的PCB中,定义输入参数和可能的拓扑范围,然后用Cadence运行每个可能的仿真组合,分析信号完整性的仿真结果,最后找到可以接受的数值范围,将其范围解释为PCB布线的约束条件,再进行PCB约束驱动布线。一般来说,前仿真也很难保证实际布线之后不出现信号完整性问题。所以在约束驱动布线后再次进行SI仿真,来检查是否符合信号完整性的要求,这是SI仿真的后仿真。在对该接收机板布线之前对地址线和数据线的拓扑结构进行了分析并做了前仿真,其拓扑结构分别如图5,图6所示。

为了检验实际布线后信号的完整性,在布线完成之后对数据线和地址线分别做了后仿真,这里只取数据线AED50和地址线AEA3的后仿真波形图,如图7,图8所示。

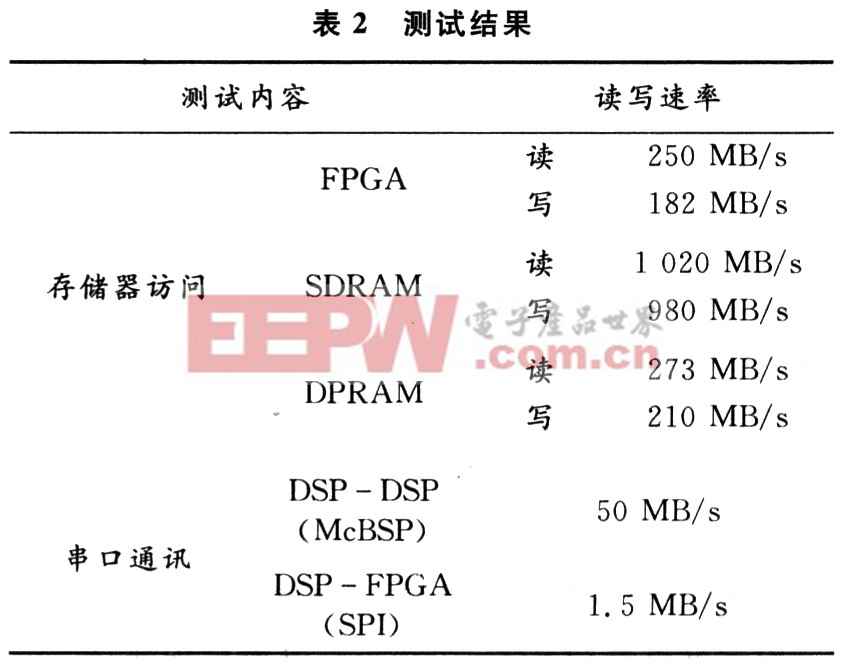

该接收机板已经设计实现。为了检测电路板的功能和性能,针对DSP和FPGA编制了所需的驱动程序,并通过各种测试程序对电路板做了大量的、长时间的各种测试。经过测试,可以确定电路板的功能已经按照设计的初衷实现,也符合接收机板要求的技术指标。另外,对电路板上各种资源访问性能的测试结果做了统计,如表2所示。

该接收机板的运算能力强,通用性强,存储容量大,可以通用于各种视频图像处理、雷达信号处理和卫星信号处理等领域,目前已应用在对处理速率和存储容量要求较高的卫星接收机技术方案中。

- 利用NI LabVIEW的并行化技术来提高测试的吞吐量(10-29)

- 基于并行接口的动态参数采集系统的设计(03-17)

- 喷墨打印机在单片机测控系统中的应用(03-01)

- 用于多站点并行测试的 ACS集成测试系统(02-27)

- LabVIEW技巧系列(二)——并行写冲突(01-05)

- labview多个并行循环同时退出(12-27)