数据采集系统中的DSP控制系统

寄存器(RBR),RBR再将数据复制到DRR中,最后等待CPU和DMA控制器读取数据。这种多级缓冲方式使得片内的数据搬移和外部数据的通信可以同时进行。

4 硬件连接电路

MAX 5633与TMS320VC5416的硬件连接如图1所示。片选CS可控制MAX 5633是否被选中。CS为低后,所有的转换开始有效。DIN为串行数据输入,SCLK为外部时钟输入。CLKSEL为时钟选择端,当C0或者该脚为高电平时,系统选择外部时钟模式,此时内部时钟模式将被关闭。所给出的硬件连接图为外部时钟模式。ECLK为外部时钟模式控制引脚,可用于控制外部时钟。RST为输入复位端。DSP的BCLK0口与D/A的SCLK相连作为MAX 5633的外部时钟,DSP的BDX0口与D/A的DIN相连作为MAX 5633的数据输入,DSP的BFSX0口与D/A的/CS相连作为MAX 5633芯片选择端。由于MAX 5633输入参考电压较多,为了尽量减小电压的波纹对其精度的影响,需要根据实际情况进行滤波。

5 软件程序设计

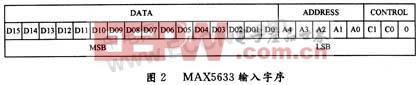

下面是针对硬件连接电路给出相应的C语言程序。该程序将MCBSP0配置成时钟停止模式(SPI)的主模式。其中SPI的时钟设置成1 MHz,帧数据长度为24位(如图2所示)。帧的24位中C0,C2为控制方式选择位;A0~A4为通道选择位,可以选择0~31共32个通道;D0~D15为需要传输的16位数据。

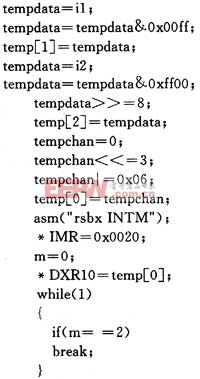

由于SPI每次传8位数据,故传输16位数据需要传3次,先传控制字,再传数据的低8位,最后传数据的高8位。系统可以通过改变tempchan选择需要传输的通道。下面是传输16位数据的代码

系统在while(1)循环过程中,等待MCBSP0口的发送中断,再将剩下的2个字节发送出去。

6 结 语

本文所介绍的方案已经取得了预期的效果,D/A的数据传输速率可达1 Mb/s,并且还可以根据实际需要进行提高。该方案已经成功地运用于系统中,使传感器稳定在它的最佳工作电压处工作。该系统中DSP对D/A的控制传输无论从精度上还是速度上均完全能够满足系统的要求。本系统所采用的模式以其高精度、多通道等特点将对以后的传感器工作电压随环境变化的系统设计具有指导意义,并对其他形式的信号采集控制系统的设计有借鉴作用。

- 基于DSP与AD9852的任意信号发生器 (11-03)

- 多通道数据采集系统(11-12)

- 基于DSP和以太网的数据采集处理系统(01-01)

- 用矢量信号分析仪检测非线性失真(04-29)

- 利用虚拟仪器进行数字信号处理设计(02-11)

- 基于μC/OS-II的电力参数监测仪设计(02-23)