基于VC++雷达信号系统软件测试平台的设计

随着电子计算机技术及电子设备的飞速发展,人们对数据的处理容量、处理速度以及工作平台的实时监控等性能的要求越来越高,从而使得高速、便捷、智能化的高性能数字处理设备成为当今电子设备的发展趋势。

由于一些气象雷达站一般地处环境与气候恶劣的偏远地区。雷达站内雷达信号处理系统的检测与维修存在一定的难度。当系统出现故障要进行检修时,由于地理环境的限制,检修在时间上会有一定的拖延,人们希望对于非硬件电路损坏的故障,能够通过软件平台进行监控,并通过软件来及时对系统进行维护与系统恢复。该软件设计的目的就是为了避开雷达系统存在着一定的机械性和不方便性的缺点来完善该雷达信号处理系统。该软件利用VC++的友好界面来实现PC机、DSP、HSP(硬件信号处理器)之间通信的可视化,利用PC机最终监控大气雷达信号处理系统中的核心部件HSP。此外,还解决了特定外部设备与PC机之间的海量数据传输问题,实现了DSP与PC机之间的优势互补。此软件平台具有一定的通用性,可以通过主机选择对不同的硬件系统的操作,下载不同的数据处理算法到DSP芯片中等,同时也可为其它不同型号DSP芯片开发软件平台提供一定参考。该软件构建了一个界面友好、实时性强、操控方便的信号处理系统,简化了测试人员的工作,同时降低了系统检修的频率,雷达信号处理器的性能得到了比较大的提高。

1 系统硬件组成及功能

整个系统的硬件结构,如图1所示,其中核心部件主要有:硬件信号处理器(Hardware SignalProcessing,HSP)、Daytona板及PC机。HSP主要完成中频I/Q数据采集、接收机、发射机控制以及定时信号产生等功能,其性能的好坏直接影响到整个雷达系统的正常运行。

Daytona板是Spectrum公司生产的DSP开发板,它的主要功能是对HSP采集的大量回波数据进行高速处理后并传送给PC机,同时处理来自PC机的数据并传送给HSP,它主要由以下几个部分组成:两片TMS320C6701 DSP、3片hurricane桥、一片DEC21153 PCI桥、3块I/O接口芯片(PEMSites、PMC Sites以及DSP-LINK3)、一片主机接口芯片HPI、128 k×32-bitSSRAM、4 M×32-bitSDRAM以及8 k×32-bit双口RAM等,其硬件结构,如图2所示。

2 基于VC++平台的软件设计

该软件平台的目的用软件来模拟一块基于PC机的硬件信号处理定时板卡,此硬件信号处理定时板卡是中国新一代多普勒气象雷达CINRAN CA和CINRAN CB系统核心部件之一,这就可以避开雷达系统存在一定的机械性及不方便性的缺点。该平台的主要功能是对Daytona板和HSP(硬件信号处理器)进行测试和控制。

2.1 软件设计思想

HSP接收并处理来自A/D变换器的数据,然后送往由双C6X DSP芯片构成的Daytona板进行处理。由两片DSP芯片来处理来自于HSP的大量的回波数据,不仅提高了数据的处理速度,而且在存储容量上也有一定的提高。经DSP芯片处理后的数据可以通过PCI总线存储到PC机中,也可以通过DSP芯片来编写无损压缩算法将大量的I/O数据处理后进行压缩,然后再存储到PC机或者DSP中,这样可以充分运用PC机平台上丰富的软件和硬件资源完成目标显示、数据融合、参数设置等任务。该软件利用VC++的友好界面显示HSP的工作状态,通过发中断命令来实现PC机对HSP的控制与监测,从而实现了PC机与DSP、HSP之间的通信;同时,通过调用Daytona板的相关软件,实现两片DSP芯片之间的数据传送及中断等。

2.2 软件设计的步骤

2.2.1 PC机与DSP之间的通信

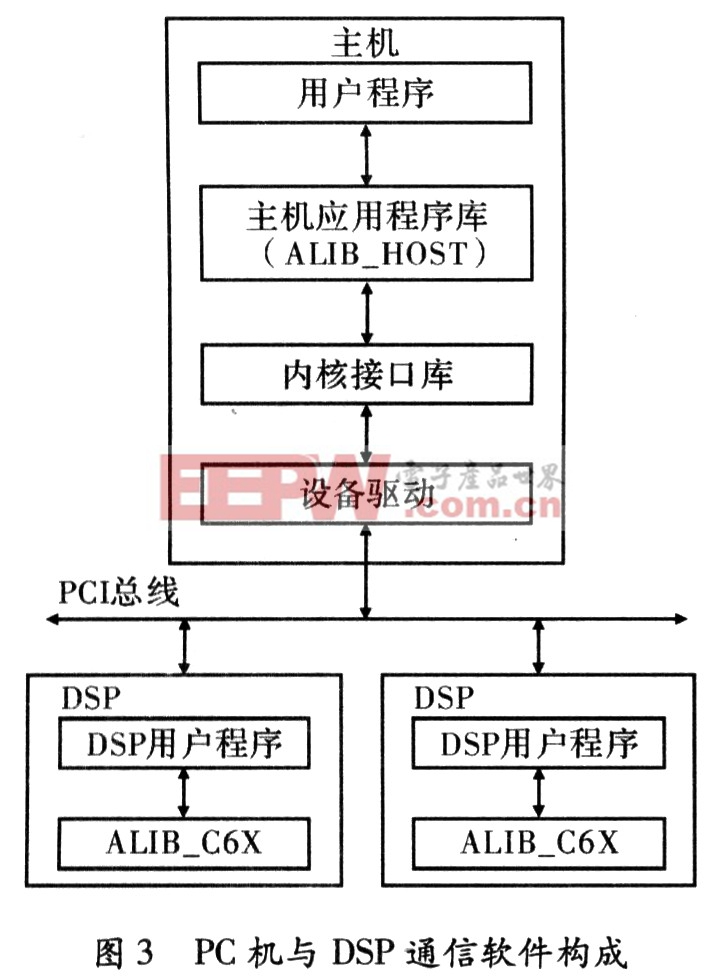

PC机通过依次调用主机应用程序库(ALIB_HOST)、内核接口库以及设备驱动程序来和Daytona板中的DSP芯片进行通信;DSP首先调用C6X应用程序库(ALIB_C6x)中的FTC6x_Init()函数对其进行初始化、设置外部存储器的等待状态以及页面寄存器的配置等,然后通过调用DSP用户程序实现与PC的通信。整个通信过程,如图3所示。

|

2.2.2 Daytona内部两片DSP之间通信过程 |

- 安森美半导体新的高集成度过压保护IC 减少便携设备电路板占用空间多达40%(10-21)

- 利用VC++模拟示波器实现简谐振动的合成(05-02)

- 某型末制导雷达自动测试系统设计(05-12)

- G.SHDSL接口卡多PVC测试技术(10-22)

- 利用VC++模拟示波器实现简谐振动合成 (02-21)

- G.SHDSL接口卡多PVC测试技术的研究(03-10)