一种2 Gsps数字示波器数据采集系统的设计

3 硬件设计

3.1 目标系统高速时钟电路的设计

通过LMX2531的标准的三线串行接口(CLK,DATA,LE)对其编程,以控制LMX2531能够输出期望的频率。时钟输出频率大小的计算公式为:

fout=N×(OSCin/R) (1)

其中,N=Ninteger+Nfractional(包括整数和小数两部分),Ninteger的值即为Ⅳ分频器的值,Nfractional的值包括NUM和DEN两部分的值,R代表R分频器的值,OSCin为参考时钟输入值。R分频器的值可以由用户在1,2,4,8,16,32中任选一个,而且参考时钟输入OSCin和输出频率fout也是用户自己决定的。根据设计要求,确定各个寄存器的具体取值,将计算好的数据写入芯片内的11个24位控制寄存器,从而得到ADC需要的1 GHz的时钟。

3.2 AT84AD001工作模式的设置

AT84AD001的工作时序如图2所示。I,Q通道ADC都使用I通道输入模拟信号,I通道工作时钟频率为1 GHz,Q通道的工作时钟与I通道工作时钟同频反相,在这种模式下,通过两个实时采样率为1 Gsps的ADC按照交替方式并行采样,将得到的数据按照一定的输出格式拼合成2 Gsps的数据流。

3.3 FPGA内部逻辑模块介绍

FPGA内部逻辑模块主要包括:

1)时基电路模块:接收AT84AD001的输出数据同步锁存时钟作为FPGA内部的工作时钟,并且为数据采集系统提供时间基准尺度。

2)数据采集接口、存储接口模块:利用

FPGA的串行收发器SERDES(Serializer/Deserializer)和动态相位对准DPA(Dynamic Phase Alignment)电路接收LVDS格式、1 Gbps速率的差分数据流,并且对其降频,然后根据差分通道和ADC数据位的对应顺序以及接收器数据的输出格式,设计恢复电路,将64位的数据按采样点的格式恢复为8个采样点,最后在FPGA与片外存储器之间建立数据存储接口,将数据按照一定的速率和格式写入片外存储器。

3)采集控制模块:利用采集状态机,配合软件系统完成对整个采集过程进行管理,按照设定的预触发和后触发数据量完成成整个采集工程。

4)触发控制模块:用来实现信号特征点的捕捉及波形显示的同步。

5)计算系统接口模块:完成FPGA和DSP之间的通信。

其中,采集状态机作为采集控制模块的核心,负责整个数据采集过程的控制,具有举足轻重的地位。它是一个用VHDL语言编制的状态机,其状态转换如图3所示。图3中状态转换所涉及的采集状态说明如表1所示。

4 数据采集系统监控软件设计

为了便于测试整个硬件的工作,在DSP中编制了简单的监控程序,程序流程图如图4所示。首先,DSP调用时钟芯片和ADC的初始化程序,完成对高速时钟电路和采集电路的初始化,使其工作在目标系统所需要的工作模式下;然后发出采集开始命令,数据采集系统进入采集过程;延迟一段时间以后,查询采集结束标志;当得知采集过程结束时,便从RAM中读取波形数据,经过分析处理后送去显示。

5 调试结果

5.1 实时采样率的分析

均是10 MHz,150 mvVpp正弦波,在软件开发环境Visual DSP++中运行数据采集系统监控程序,得到通道1和通道2的采样数据,利用VDSP中的调试工具分别以通道1和通道2的采样数据作为数据源,经过通道校准,调整每一通道的模数转换器所包含的双通道ADC之间的偏移和模拟信号增益存在的差别。选取任意400个采样点以折线图的形式恢复出采样波形,如图5所示。

从采到的波形数据提取连续400个采样点恢复出波形,正好显示了两个信号周期,另外恢复出的波形的幅度与信源幅度相符合,可以得知通道1、通道2均实现了2 Gsps的实时采样率。

5.2 有效位数(ENOB)的分析

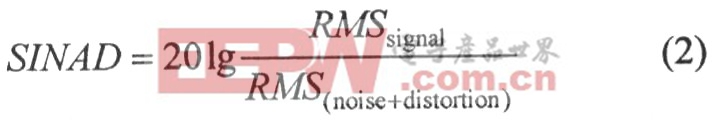

有效位数(ENOB)是衡量数据采集系统动态特性的一个最为重要的指标。计算公式为:ENOB=(SINAD-1.16 dB)/6.02 。 SINAD是信号幅度的均方根值与从直流到fs/2的带宽内所有其他频谱成分的均方根值的比值(包括谐波但不包括直流成分)。其计算公式为:

通道1、通道2的输入信号均是10 MHz,330 mVVpp的正弦波,在VDSP中运行数据采集系统监控程序,得到通道1和通道2的采样数据,从每个通道的采样数据中各取任意连续1 024个采样点作为测试数据,利用Matlab编程,计算其有效位数(ENOB)分别是:6.71(通道1),6.77(通道2)。由以上计算结果得知该数据采集系统具有较高的量化分辨率。

6 结论

通过实验板硬件调试与软件仿真,设计了双通道同时工作,每通道最高实时采样率为2 Gsps,分辨力为8 bit,存储深度8 MB/CH的数字示波器数据采集系统,并且验证了实验板上的数据传输和数据存储均能满足2 Gsps数据采集系统的要求。

- 一种用于同步多个GSPS转换器的测试方法(12-23)

- 一种数字示波器的微处理器硬件设计(09-08)

- 基于AT89S52单片机的简易数字示波器设计(07-26)

- 利用数字示波器调试嵌入式I2C总线(10-03)

- 利用数字示波器调试嵌入式I2C(10-16)

- 使用数字示波器完成EMI预测试(05-06)