借助智能DAQ, 获得高级数据采集技术

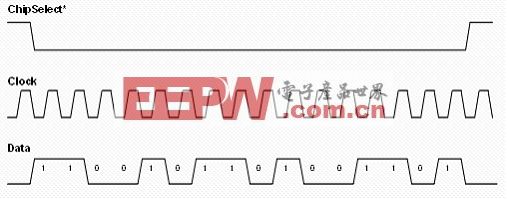

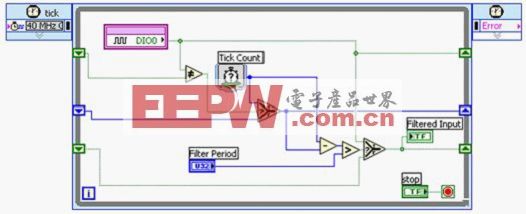

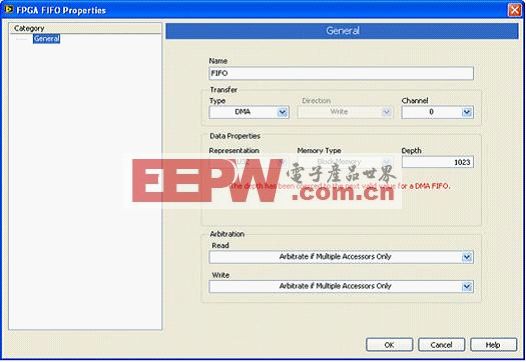

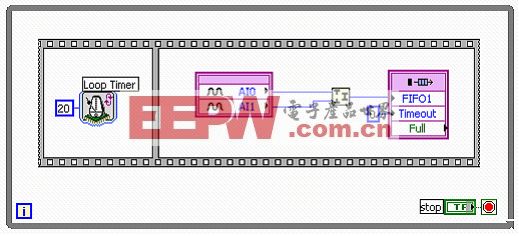

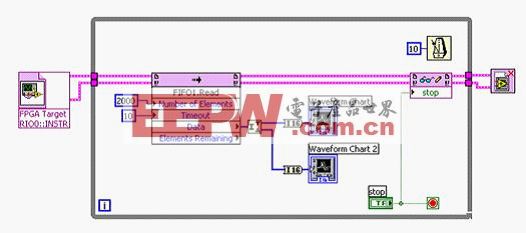

的生成和配有NI-DAQmx的暂停触发器 在NI LabVIEW FPGA中,暂停触发器无需接受配置,因为只需简单的条件结构便能在硅芯片中实现相同的功能。 此处是通过智能DAQ运行时所展现的相同功能(图14)。 图14. 连续脉冲序列的生成和配有智能DAQ的暂停触发器 在这种情况下,数字I/O线DIO0用作暂停触发,而脉冲将在数字I/O线DIO1上生成并输出。使用单周期定时循环可令各个脉冲获得25 ns的分辨率,因为这将成为单个计时在使用40 MHz定时源时的值。 数字I/O应用 智能DAQ硬件提供多达160条硬件定时数字线,令诸多数字应用成为可能。 我们已经学习了如何使用数字I/O实现触发、同步及计数器/定时器的运行,而智能DAQ还可用于误码率测试、数字模式匹配、脉冲宽度调制、正交编码器和数 字通信协议。 自定义或标准形式的串行接口均能直接通过数字定时框图编程来实现。 举例说明,SPI便是一款与硬件组件(如:微控制器或ADC)进行通信时最常用的串口协议。 图15(下图)展现了在进行16位SPI通信时,3条必要数字线所对应的定时框图。 图15. SPI通信输入定时框图 如定时框图所示,所有16位数据均在每个时钟周期上顺次传递,而片选控制线(chip select line)则呈现低电平。 现在,我们来看看在NI LabVIEW FPGA中,如何通过智能DAQ硬件上的3条数字线进行此类编程。 图16. 16位SPI通信程序框图 图16中,外部While循环确保了所有代码均能连续执行,而写入布尔输入控件则通过条件结构启动着数据传递。 顺序结构中的第一框架将片选控制线(chip select line)设置为低电平,之后由中间框架写入数据位并将时钟线切换16次。 最终,第三顺序框将片选控制线(chip select line)设置回TRUE状态,并将数据线重置为默认的FALSE状态。 这一简单范例只是借助智能DAQ进行数字通信时的一项内容。 用户若想应用数字握手,便需为ACK(备用)和REQ(暂停)线准备2路通道,其中一路通道面向并行运作的时钟信号和数据线。 数字线会时常抖动,在使用机电接触时更是如此,然而用户可通过NI LabVIEW FPGA,选择不同方式,在数字输入线上添加去抖动滤波器。 在消除状态的错误改动时,数字去抖动滤波器确保数值的变化能够保持一段最短的时间,因而规避了因抖动引发的错误读取。 图17展现了如何通过智能DAQ实现此项功能的内容。 图17. 智能DAQ硬件上的数字滤波器程序框图 数据传输方式 配备NI-DAQmx驱动程序的传统多功能DAQ和智能DAQ之间的最大差异在于:数据传输的执行方式。 NI-DAQmx驱动程序将承担由设备至主机的各项传输任务,此项操作中NI LabVIWE FPGA会对基于FPGA的所有板载硬件进行编程。 用户可通过多种途径缓冲设备上的板载数据,并使用不同方式(如:DMA通道或中断请求)传输数据。 NI LabVIEW FPGA中的FIFO缓冲区在LabVIEW项目浏览器中接受配置,并能借助板载内存或硬件逻辑获得运行。 图18显示了如何经由项目浏览器,在板载块存储器中配置整数的FIFO缓冲区。 图18. NI LabVIEW FPGA中的FIFO配置 FIFO一经创建,便能用于NI LabVIEW FPGA程序框图上多个循环之间的数据传递。 图19中的范例显示:数据先被写入左侧循环中的FIFO,并随即从右侧循环中的FIFO被读出。 图19. 通过FIFO和多循环实现的NI LabVIEW FPGA程序框图 同样通过LabVIEW FPGA FIFO获得应用的直接存储器访问(DMA)通道,在项目浏览器中接受了类似的配置。 图20. NI LabVIEW FPGA中的DMA FIFO配置 图21. 通过DMA FIFO和位组装实现的NI LabVIEW FPGA程序框图 所有的DMA FIFO数据传输宽度均为32位;因此,当其传递源自16位模拟输入通道的数据时,往往能够合并2路通道或2个样本上的数据再进行传输,从而提高带宽使用 率。 这即是图21所展现的位组装。当数据被直接传递到主控计算机的内存后,便可通过在Windows环境下运行的NI LabVIEW主接口函数接受读取(图22)。 图22. 通过DMA FIFO读取和位拆装实现的主接口代码 如图22所示,主接口程序框图引用FPGA终端VI,然后使用While循环连续读取DMA FIFO。 32位的数据被分解为2路16位通道,在波形图表上接受采样和绘制。 主接口VI还能对FPGA VI前面板上的各类显示控件和输入控件进行读写操作;在这种情况下,“停止按钮”输入控件也被写入。 结论 尽管DAQ-STC2等固定ASIC能够满足数据采集的大多数需求,然而,唯有借助智能DAQ中基于可重新配置FPGA的I/O定时和控制,方能实 现高度灵活性和完全定制。 借助NI LabVIEW FPGA,触发和同步任务获得了简化,因为通过绘制图形化程序框图即可充分满足用

- 采用模块化仪器,对新兴音频和视频应用进行测试(02-19)

- NIDays2008新技术新体会——多核技术下LabVIEW编程(10-21)

- 你知道吗?——NI也是08年北京奥运会的幕后功臣之一(10-17)

- LabVIEW8.6有哪些新亮点?(10-17)

- 使用虚拟仪器降低测量成本(11-06)

- NI FlexRIO适配器模块开发工具集(MDK)包含哪些内容?(01-06)