应用LPC2131开发PLC调速器测频单元

关键词: PLC调速器; 测频单元; LPC2131; 串行通信

在水轮机调速器中,机组频率的测量直接关系到调速器整机性能的优劣,而调速器的品质与性能直接影响到电能的品质和水电站的安全可靠运行, 故机组频率的测量是一个非常关键的技术[1]。目前,基于PLC调速器的测频方法主要有单片机测频和PLC本体高速计数模块测频2种方式[2]。PLC

取自发电机端电压互感器和电网电压互感器的测频输入信号,经削波、滤波处理后,变成幅度基本不变的稳定波形,再经施密特电路放大整形,得到正负幅值基本相等、占空比约为50%的方波[4];然后,通过光电耦合器将输出的机组频率和电网频率方波信号隔离后分别送入LPC2131微控制器CAP1.3功能捕获引脚P0.18和CAP1.2功能捕获引脚P0.19。CAP1.3和CAP1.2捕获功能设置为上升沿与下降沿同时捕获,即这2个功能引脚上的值由0到1跳变和由1到0跳变都会将当时计数器值输入相应的捕获寄存器中,同时产生中断。对任一路管脚捕获,取出2个相间隔的捕获寄存器值相减,令其差值为N,在计数器频率(时钟频率,令其为Fpclk)已知情况下,可得出2个相间隔捕获点对应时间值,即频率信号周期值:

根据频率与周期公式f=1/T可求出信号的频率值。对得到的机组频率和电网频率计数器差值采用去极大极小值进行简单的判断滤波后,采用自由口通信协议通过串口UART0将其发送至PLC,在PLC控制器内完成机组和电网频率值计算。

2 测频硬件与软件

2.1 LPC2131微控制器

LPC2131是PHILIPS公司基于ARM7TDMI-S核、单电源供电及LQFP64封装的微控制器,是基于一个支持实时仿真和跟踪的16/32位ARM7TDMI-S型CPU的微控制器。LPC2131拥有2个符合’550工业标准的异步串行口UART0和UART1,具有以下特性:16字节收发FIFO;寄存器位置符合16C550工业标准;收发器触发点可为1、4、8和14字节;内置波特率发生器;包含使能软件流控制器。LPC2131还带有2个32位可编程定时/计数器,均具有4路捕获和4路比较匹配与输出电路。定时器对外设时钟(pclk)周期进行计数,可选择产生中断或根据4个匹配寄存器的设定,在达到指定的定时值设定时执行其他动作。它的4个捕获输入,用于在输入信号发生跳变时捕获定时器的瞬时值,并可选择使捕获事件产生中断[5]。

2.2 LPC2131微控制器定时器模块

LPC2131微控制器定时器方框图如图2所示。定时器控制寄存器TCR用来使能或者复位计数器操作;预分频寄存器PR用来分频时钟计数频率;VPB时钟频率Fpclk为计数提供时钟频率;预分频计数器PC是当TCR使能后,在每个pclk周期加1,当其达到预分频寄存器PR中保存的值时,定时器计数器TC值加1,预分频计数器在下一个周期复位;当预分频计数器达到上限时,定时器计数器TC值加1,当达到计数上限0xFFFFFFFF后将翻转到0x00000000;捕获寄存器与1个对应的器件引脚相关联,当引脚发生特定事件时,可将定时器计数的值装入该寄存器;捕获控制寄存器CCR用于当捕获事件发生时,确定是否装入4个捕获寄存器中的1个,以及是否产生中断。

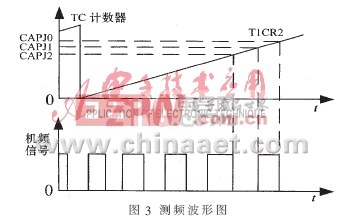

本文选用定时器1作为两路脉冲输入捕获计数器,利用它的两路脉冲捕获功能CAP1.2和CAP1.3捕获经整形后机组频率和电网频率的上升沿和下降沿信号,以CAP1.2为例,如图3所示。通过CAP1.2捕获功能,可以将每次上升沿和下降沿到来时对应的计数器值装载到T1CR2寄存器中,将连续3次捕获时计数器值依次保存到CAPJ 0、CAPJ 1和CAPJ 2 3个定义存储单元中,储存单元对应值为CAPJ 0、CAPJ 1和CAPJ 2,每完成1次T1CR2装载即可求得1次相邻上升沿或下降沿计数器差值TJ=CAPJ 0-CAPJ 2。本文设定计数时钟不分频,根据测周法原理,机组频率值Fg为:

式中, Fpclk为VPB时钟频率,在不分频情况下为11.059 2 MHz。设机组频率为Fg=50 Hz,则周期Tg=0.02 s,测得的周期数Ng=0.02×11 059 200=221 184,测频系统的理论分辨率为0.002 6 Hz,由此可见,此方法具有很高的分辨率。

2.3 测频软件流程

系统软件由1个主程序和2个中断子程序组成,如图4所示。CAPJ0、CAPJ1和CAPJ2依次保存连续3个机组频率信号捕获对应的寄存器值T1CR2,CAPX0、CAPX1和CAPX2依次保存连续3个电网频率信号捕获时对应寄存器值T1CR3,TJ和TX分别表示机组频率和电网频率在1个周期内计数器计数差值。

- 8051、ARM和DSP指令周期的测试与分析(04-19)

- 基于I2C总线的多点温度采集系统 (06-14)

- 基于P89LPC932超声波测距仪(07-09)

- 专用芯片ATT7022C的电参数测量模块设计(10-21)

- 用梯度均值法提高LPC2138的模/数转换器的分辨率 (01-10)

- 便携式功率分析仪设计-----硬件设计(三)(04-21)