基于高速A/D转换器的视频数据采集系统

摘要:针对视频采集系统需要对摄像头输出的复合视频信号进行快速转化、采样、存储的要求,设计基于高速A/D转换器TLC551O的视频采集系统。模拟视频信号通过A/D转换器转化为8位灰度值,16位微处理器MC9S12DG128B通过普通IO口,控制FIFO存储器uPD42280写入和读取A/D转换结果,实现视频图像数据的高精度采集。分析了主要芯片的工作原理及时序,描述了软件控制图像数据采集流程。并将采得数据经过处理,与实际图像对比。实验结果表明,该系统在单行扫描时问50μs内能采集160个以上的有效像素点,成像质量高,能满足简单图像处理算法对数据的要求。

关键词:A/D转换器;FIFO存储器;时序;视频图像数据

国内外的视频图像采集方法很多,基本分为两大类:自动图像采集和基于处理器的图像采集。自动图像采集多采用专门的视频解码芯片,如SAA7113,TVP5150等,自动完成模数转化,并输出行、场信号以实现存储器地址产生,一般以DSP为主处理器,除了对采集模式进行初始化设置外,主处理器不参与采集过程。这种方法的优点是采集不占用CPU的时间,实时性较好,适合于对图像数据的精度要求较高和算法复杂的场合,如车道识别、车辆识别等方向的应用。但是该方案对处理器的速度有很高的要求,成本较高,且电路复杂。基于处理器的图像采集则采用视频同步信号分离芯片产生行、场中断信号,用微处理器内部的A/D转换器实现图像的采集。图像的采集过程在CPU控制下完成,由CPU启动A/D转换,得到转换数据。该方案的特点是电路简单,成本低,易于实现,能满足简单图像采集系统的需要。但数据采集占用CPU时间,采集速度受微处理器A/D转化时间限制。

本文提出了基于独立的高速A/D转换器TLC5510的视频采集系统设计方案,能高速采集较高精度的视频数据,可适用于智能车比赛、室内导盲、车队仿真平台、移动机器人平台等道路环境相对单一。图像处理算法简单的场合。

1 系统架构

本系统主要适用于符合PAL制式的模拟摄像头输出视频信号的采集。一般的模拟摄像头的主要工作原理是:按一定的分辨率,以隔行扫描的方式采样图像上的点,当扫描到某点时,就通过图像传感芯片将该点处图像的灰度转换成与灰度成一一对应的电压值,然后将此电压值通过视频信号端输出。同时,视频信号端输出还隐含了场同步信号、行同步信号、奇偶场同步信号等信息,因此实际输出的是复合视频信号。

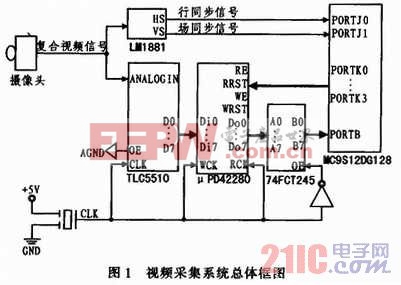

本系统采用MC9S12DGl28B作为处理器,针对信号特点,主要设计思想如下:首先,通过专门的视频同步信号分离芯片LM1881提取复合视频信号的行同步脉冲、消隐脉冲和场同步脉冲,并将它们转换成数字式电平直接输给单片机的中断口作为控制信号。同时采用高速A/D转换器TLC5510对视频信号进行A/D转换,使视频电压模拟信号转换为代表图像灰度的数字信号输出。接着采用FIFO存储器uPD42280作为视频数据的缓存,在行中断服务函数中对其进行写控制,将A/D转换数据写入其内存中。最后,当一场图像结束时,在场中断服务函数中通过单片机的8位IO口将视频数据读回。为了保证数据的稳定,在单片机与FIFO存储器之间加了一级74HC245,作为数据缓冲。为保证采集同步,LC5510 uPD42280和74HC245采用同一有源晶振作为转换和读写的时钟源。本系统框架如图1所示。

2 系统硬件设计

视频采集系统一场图像时间内的采集数据量决定了成像质量,也就是常说的分辨率或者叫像素。按照我国PAL制式的信号特点,每秒扫描25帧图像,每一帧图像又分奇偶两场,那么,一场图像的扫描时间就是20 ms。目前市场上的摄像头,不管是CCD或是CMOS成像的,纵向分辨率基本都在400线的以上。因此推得单行视频信号的持续时间小于20 ms/400=50μs左右。那么,如何在50μs内对视频信号进行快速地A/D转换,得到更多的灰度值数据,以提高横向分辨率就成为视频采集系统设计的关键问题。

2.1 高速A/D转换器

TLC5510是美国TI公司生产CMOS,8位高阻抗并行的模数转换器件(ADC)。它采用+5 V单电源工作,能提供的最大采样率为20 MSPS。TLC-551O的满输入量程是2 V,TLC551OA的满输入量程是4 V。TLC5510采用了半闪速结构及CMOS工艺,所以大大减少了器件中比较器的数量,并在高速转换的同时能够保持较低的功耗。在推荐的工作条件下,TLC5510的功耗仅为130 mW。

TLC5510模数转换器内含时钟发生器、内部基准电压分压器、1套高4位采样比较器、编码器、锁存器、2套低4位采样比较器、编码器和1个低4位锁存器等电路。TLC5510的外部时钟信号CLK通过其内部的时钟发生器可产生3路内部时钟,以驱动3组采样比较器。基准电压分压器则可用来为这3组比较器提供基准电压。输出A/D信号的高4位由高4位编码器直接提供,而低4位的采样数据则由2个低4位的编码器交替提供。 TLC551O的工作时序如图2所示。时钟信号CLK在每一个下降沿采集模拟输入信号。第N次采集的数据经过2.5个时钟周期的延迟后送到内部数据总线上。此时如果输出使能端OE有效,则数据可送至8位数据总线上。

- 用梯度均值法提高LPC2138的A/D分辨率(01-06)

- AD7677在变送器校验装置直流测量系统的应用(01-09)

- 基于生产者/消费者设计模式的连续音频信号采集系统(05-03)

- 基于AT89S52多路数据采集系统的设计(08-22)

- 基于铂电阻的数字温度测量系统设计(04-03)

- 温度传感器在火灾报警系统中的应用(04-03)