一种多路图像采集系统的软件设计

,检测到SAV信号或EAV信号,提取H、F、V信号。然后发出开始命令,同时开启行列计数器

计数器

计数器是一种具有多种测量功能、多种用途的电子计数器。它可以测量频率、周期、时间间隔、频率比、累加计数、 计时等;配上相应的插件,还可以测量相位、电压等。一般我们把凡具有测频和测周两种以上功能的计数器都归类为通用计数器。 [全文]

,开始对接下来的图像数据进行解码,根据每个8位数据自身带的信息,判断该数据为Y,Cr还是Cb,从而得到Y,Cr,Cb各分量的值。解码流程如图4所示。

图4 解码流程

4 帧存储控制器与LCD/VGA显示控制器的设计

4.1 数据格式的转换

根据前面第2节的介绍,从ITU656解码模块出来的数据为8位4:2:2的YUV空间图像数据,而LCD/VGA显示器只能接收RGB数据。因为Y-CrCb4:2:2格式不能直接转换为RGB,所以需要先转换为YCrCb4:4:4格式。

我们知道解码芯片得到的视频数据是顺序为Cb,Y,Cr,Y,Cb,Y,Cr,……的序列,存储的时候将一个Y与一个C(Cb或Cr)结合起来组成一个16位的数据。而当数据被读出来时就要将这些视频数据转换为每个像素占24位(Y、Cb、Cr各占8位)的4:4:4的数据流。4:2:2到4:4:4的转换采用最简单的插值算法,在采样的时候,每隔一个像素才采一次色度值(Cb和Cr)。在转化时,直接将前一个有色度信息的像素点的Cr以及Cb的值直接赋给后一个像素的Cr和Cb,这样就能得到4:4:4的像素数据,每个像素占用24位位宽。

4.2 帧存储控制器

作为系统的重要组成部分,帧存储控制器主要用来进行有效数据的缓存。视频数据在FPGA1的控制下乒乓写入两片SRAM。乒乓技术应用的关键在于乒乓切换信号frame的产生,本系统中根据视频解码芯片的奇偶场信号RTS0来产生帧切换frame信号,也就是一个RTS0周期切换一次。一个RTS0周期由一个奇场和一个偶场组成,是一副完整的画面。当frame为1是,FPGA通过计数器的计数截取最终显示所需要的有效的像素点信息按照SRAM的控制时序写入SRAM1,同样当frame为0时,将对应的像素信息写入SRAM2,如图5所示。

图5 乒乓存储示意图

系统加电的同时,4片视频解码芯片同时工作,为了保证数据采集的准确性和显示的同步性,系统内生成一个八倍于像素时钟的写时钟信号write_clk,这样,在一个像素时钟周期,写时钟信号已经过了八个周期,而每两个周期分别完成一路图像数据的写过程。

由于SRAM是一维存储空间,一个地址对应一个数据。所以在写入数据时将SRAM的地址空间划分为4段,每一段用来存储一路图像数据。

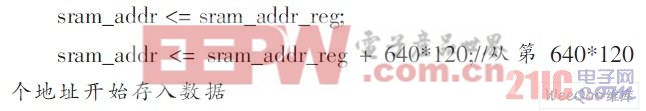

用程序实现比较简单,设置一个地址寄存器sram_addr_reg,将它赋给SRAM的地址控制信号sram_addr。然后在对每一路图像写入时,将对应的SRAM的起始地址加上一个固定的基数。如:

这样就保证了SRAM中对应地址的数据和屏幕上显示位置的一一对应关系,在读程序中,只需要按照顺序读SRAM即可,如图6所示。

图6 SRAM地址验证

4.3 LCD/VGA显示控制器

本模块主要是用FPGA来产生LCD/VGA显示时所需要的时钟信号CLK(像素时钟信号)、VSYNC(帧同步信号)、HSYNC(行同步信号)和使能信号(VDEN),并在相应控制时序的作用下,依次将显示缓存即SRAM中的数据依次读出,输出到LCD上的过程。

LCD显示所需的主要时序信号的关系如图7所示。

图7 LCD时序信号图

在系统中,LCD屏幕分辨率为640x480,像素时钟CLK为25MHz,由于FPGA的主时钟输入选用了20 MHz的有源时钟,那么就要求利用Cyclone芯片的内部逻辑资源来实现时钟倍频,以产生所需要的CLK(25 MHz)、用Verilog语言编写参数化的时序生成模块,产生HSYNC(32 kHz)及VHY-NC(60 Hz)时钟信号,如图8所示。

图8 时序验证

VGA显示原理与LCD相似,除了在硬件上正确连接ADV7125芯片电路外根据需要的分辨率来生成相应时钟信号即可。

5 图像抖动的分析与解决

在系统完成后软硬件联调时,出现画面抖动现象,其中以RTSO为基准而产生乒乓切换的那一路图像稳定,其他三路都出现不同程度的抖动现象。对此我们做了深入的分析和实验,分析整个系统的结构可知,系统在多个时钟控制下共同工作,也就是所说的典型的异步系统。我们知道,数据在异步系统传输时对时钟要求非常严格,稍微的一点时钟偏差都会带来对有效像素截取的偏差,最终影响图像的显示质量。

解决的办法有两个,一是加入缓冲机制,利用FIFO对数据存储的特性来实现数据在异步时钟之间的无缝传输;二是同步时钟,利用状态机等方法使得异步系统的时钟能够尽可能同步。采用第二种方法对系统进行改进,首先系统中所有的分频、倍频尽量使用Quartu

- 基于C8051F020单片机的多路压力测量仪(01-23)

- 基于FPGA的160路数据采集系统设计(03-22)

- 智能多路信号源的设计与实现(01-10)

- 基于单片机的多路测温仪系统设计(05-09)

- 使用模拟多路复用器的多通道电流测量技术(02-27)

- 用Pico2204A彻底分析视频多路混合器系统的问题(01-12)