基于DSP的高速数据采集系统硬件设计

2.3 JTAG电路

JTAG是基于IEEE 1149.1标准的一种边界扫描测试方式(Boundary-scan Test),结合仿真器和仿真软件,可访问DSP的所有资源,包括片内寄存器以及所有的存储器,从而提供实时的硬件仿真与调试环境,便于开发人员进行系统调试。在大多数情况下,如果开发板和仿真器之间的连接电缆不超过6英寸,可以采用图4的接法。但应该注意,DSP的EMU0和EMU1引脚都需要上拉电阻,推荐值为4.7 kΩ或者10 kΩ。如果DSP和仿真器之间的连接电缆超过6英寸,则需要另加缓冲驱动电路。

2.4 时钟电路

TMS320VC5509的外部时钟从CLKIN引脚输入,在内部修改这个信号,来产生希望频率的输出时钟,时钟发生器将这个输出时钟(即CPU时钟)送给CPU、外设和其他的内部模块。也可以用可编程的时钟分频器对CPU时钟分频,在CLKOUT引脚输出。时钟发生器中还有一个时钟模式寄存器(CLKMD),用来控制和监视时钟发生器,它可以控制时钟发生器进入两种工作模式:

1)旁路模式,PLL被旁路掉,输出时钟的频率就等于输入时钟的频率除以1、2、4。

2)锁定模式,输入时钟既可以乘以或除以一个系数来获得期望的输出频率,并且输出时钟相位与输入信号锁定。

在锁定模式下,输出频率由下面的公式计算:

输出频率=(PLL MULT/(PLL div+1))×输入时钟频率

在此,可以选择时钟发生器工作在锁定模式,即CLKMD的PLL ENABLE为1,外部振荡晶体可以为10~20 MHz。根据外部振荡晶体与DSP内部时钟信号,可以计算出相应的PLLMULT与PLL div值,图5为DSP的外部时钟电路。

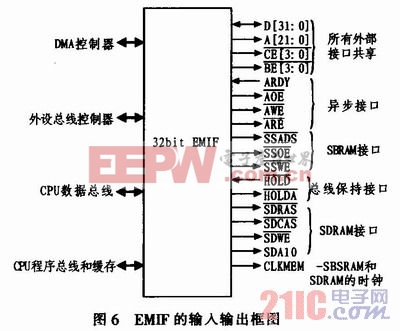

2.5 DSP外扩存储器

在TM320VC5509芯片中,有一个外部存储器接口(EMIF),它为3种类型的存储器提供了无缝接口:异步存储器,包括ROM,FLASH以及异步SRAM;同步突发SRAM(SBSRAM),工作在1倍或1/2倍CPU时钟频率;同步DRAM(SDRAM),可以工作在1倍或1/2倍CPU时钟频率,可以根据系统需要扩展存储器。图6为EMIF的输入输出框图。

比如,可以对DSP进行FLASH扩展,可以将FLASH作为其外部程序存储器,供DSP上电时启动载入程序(BOOTLOAD)使用,其作用是将FLASH中保存的程序载入到DSP中运行。在与DSP的连接上,可以将FLASH的地址和数据总线连接到DSP的EMIF接口总线上,FLASH的片选信号连接到DSP的CE1引脚,配置成CE1空间,CE1引脚在上电复位后为低电平。此外,FLASH的读写信号分别连接到EMIF接口的读写信号引脚上。

当然,根据系统的需要,也可以利用EMIF接口对其他存储器进行外扩,具体方法可查阅相关技术手册。

2.6 其他外围硬件电路

1)根据系统的要求,可以对DSP系统扩展液晶显示模块,目前,液晶显示模块型号众多,用户完全可以根据自身需要选择一块适合的液晶显示模块。

但是由于LCD是典型的慢速设备(相对于DSP来说),在和高速微处理器接口时,会耗费大量时间,这是不允许的。如果DSP处理余量较小,可以考虑采用CPLD在DSP和LCD之间设计一条双向的快速通道,来实现对LCD的控制,也就是说,把DSP处理完的数据送给CPLD,然后由CPLD来控制并模拟LCD的读写时序来完成数据的显示,这样可以大大节省DSP的资源。

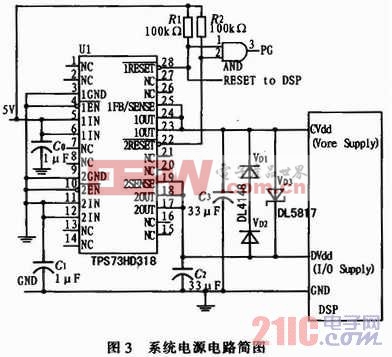

2)在系统的开发板上,可以加入信号灯,用于指示最小系统的的电源情况,当电源指示灯出现异常时可及时断电。以保护电路不被损坏。通常,可以设置+5 V的电源指示灯(电路板供电正常)、电压转换输出3.3 V指示灯(I/O供电正常)、电压转换输出1.8 V指示灯(内核供电正常)以及其他信号指示灯。

3 总结

本文简单介绍了以TMS320VC5509芯片为核心处理器的数据采集系统的主要硬件设计,在实际应用中,应该根据系统需要,具体设计合适的硬件电路,然后在进行软件和算法方面的编写,最后达到系统要求。

另外,根据不同信号处理的要求,还可对系统进行进一步完善:如增加USB控制器、完善总线功能及对扩展外存的进一步研究等,从而使系统更加广泛地应用于复杂工程领域。

- 基于DSP与AD9852的任意信号发生器 (11-03)

- 多通道数据采集系统(11-12)

- 基于DSP和以太网的数据采集处理系统(01-01)

- 用矢量信号分析仪检测非线性失真(04-29)

- 利用虚拟仪器进行数字信号处理设计(02-11)

- 基于μC/OS-II的电力参数监测仪设计(02-23)