组合压缩在存储测试系统中的应用

3.2 算法的FPGA实现 3.3 结果与分析

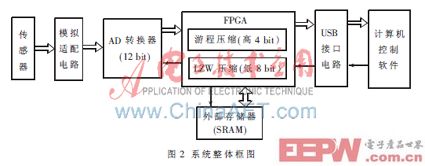

系统的设计核心是压缩算法实现。由于游程压缩实现简单,下面重点讨论LZW算法的实现。用FPGA实现LZW算法要解决以下几个问题[6]:

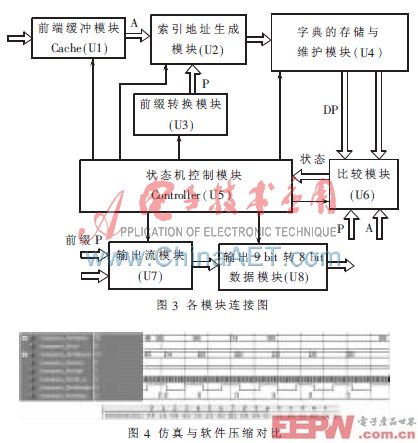

(1)压缩过程中字典的缓存。因为所有数据处理和传输工作都是由FPGA 完成,字典的缓存必须使用FPGA内部有限RAM 资源。(2)字典的建立与更新。字典的建立使用FPGA 片内资源来完成, 大容量字典虽然会提高压缩比,但必须考虑到FPGA内部的资源量。因此选用9 bit的定长编码方式对数据进行处理。(3)压缩后输出数据流的传输和存储。由于压缩后是9 bit的数据流,不利于数据的存储。因此需将9 bit的数据流转换成8 bit的数据流进行传输和存储。FPGA设计过程中模块划分非常重要,好的模块划分能够大大减少逻辑所消耗的面积和优化功能的时序关键路径。LZW算法实现划分了8个模块,各个模块相互之间的连接如图3所示。整个压缩过程都是在状态机控制模块(U5)下进行的。

本文对所实现压缩算法进行了综合与仿真验证,使用开发工具为Altera公司的QuartusII 7.2,使用Modelsim SE 6.1f仿真工具,用图4所示的字符串作为输入码流进行测试。图中datain表示输入数据,dataout表示压缩输出码流,以16进制表示,用于验证压缩的正确性。仿真结果与通过计算机软件压缩的结果完全一致。如图4所示,本设计完全可行。

经过综合, 算法的实现使用了20个引脚,占用了13%的逻辑单元,使用了33%的内部RAM存储容量,综合所得最高时钟工作频率为80 MHz,实时压缩速度达到8 MB。表2是一组实测数据的压缩效果。

本文介绍的在以FPGA为核心的存储测试系统, 实现了数据的无损组合压缩。通过相关仿真和综合验证, 压缩效果显著,大大减少了对存储空间的要求,实现了压缩性能与压缩速度的统一。算法主体结构用VHDL语言编写, 具有可移植性,可广泛地应用于各种基于FPGA的数据压缩系统中,有很大的应用价值。

参考文献

[1] 张文栋.存储测试系统的设计理论及其应用[M].北京:高等教育出版社, 2002.

[2] 吴家安.数据压缩技术及应用[M].北京:科学出版社, 2009.

[3] 朱琳,罗家融,田一海.核聚变实验数据采集系统中数据压缩算法的研究[J].计算机工程,2003,2(29):11-12.

[4] MARK N. LZW data compression[EB/OL].1989.http:marknelson.us/lzw-data-compression/.1989-10-01.

[5] Altera Corporation. Cyclone II device handbook,volume 1. 2007.

[6] 陈晋敏,黄春明,周军.激光雷达数据无损压缩的FPGA实现[J].计算机测量与控制,2007,15(1):100-102.

组合压缩 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)