利用时钟裕度技术早期故障预测

为了成功实现时钟裕度功能,其必须内置频率调节的功能。变频功能在实际上可能比最初设想的要更困难,因为我们必须全面了解锁相环技术的性能,不仅要了解工作期间可以实现的目标频率,还要了解不同反馈编程条件下的相位噪声与抖动性能。基于时域的抖动是我们需要了解的重要内容,这样才能确保不同频率之间的一致性(不能突然断开),否则系统的稳定性分析就会出错。如果发生了不连续的抖动情况,也不会出现太大麻烦,可以通过多个特定的输出频率开槽或所需的分频比来解决。此外,应当确保开槽不要在频率变化期间进行,除非锁相环的设置在CPU对任何形式的开槽和短脉冲不敏感的间隔中进行。

确保总时序预算正确的技巧就是,应当了解哪些频率范围表现较好,这样就能小心地通过逐步逼近的办法接近总时序预算目标,而每一步的变化量可能有差别。如果频率变化较大,那么通常会导致总时序预算差别结果较小。总时序预算边界检测要求最终肯定要突破系统的界限,然后重启并略微后退一些,直至获得满意的一致性阈值为止。有许多没有文件记载的“小窍门”可以完成此项工作。建立系统总时序预算的关键就是一致性与可重复性。

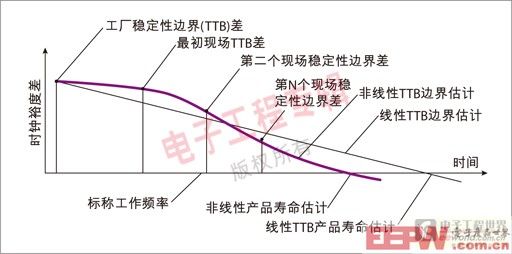

正如前面简单谈到的那样,执行时钟裕度工作所发现的最重要信息就是在产品投入使用后估算出实际的产品使用寿命终结时间。本文分析的目的就是要通过时钟裕度来计算产品的标称性能与总时序预算之间的差异,以备后续之需。在几周、几个月乃至几年的时间里,投入实际使用的产品运行相同的回归进程,重复计算性能差异。我认为,能够体现产品使用寿命结束的情况就是在性能差为零或为负值。这并不是说系统出现故障,而只是说没有性能差了,说明产品已经到了使用寿命的终点。无论采用何种产品支持方式,如果性能差为零,则说明产品的使用寿命已经结束了,这一信息对那些需要全天候持续工作的系统来说是至关重要的。如图1所示,根据历史性能差信息预测出了性能差为零的时间。通过简单的线性分析或非线性曲线分析,可以估计得出产品使用寿命结束的时间。

图 1:系统使用寿命估算分析图。

在温度与电压等外部因素已知、记录且匹配的情况下进行未来回归检测,确保符合时钟裕度技术的准确性。图1显示了超频工作情况下的时钟裕度性能差为正值的变化图,此原理也适用于降频工作的情况。不过,在降频工作情况下,性能差的变动不会太大且基本保持稳定。这里将降频工作情况下的时钟裕度差值设为正值。

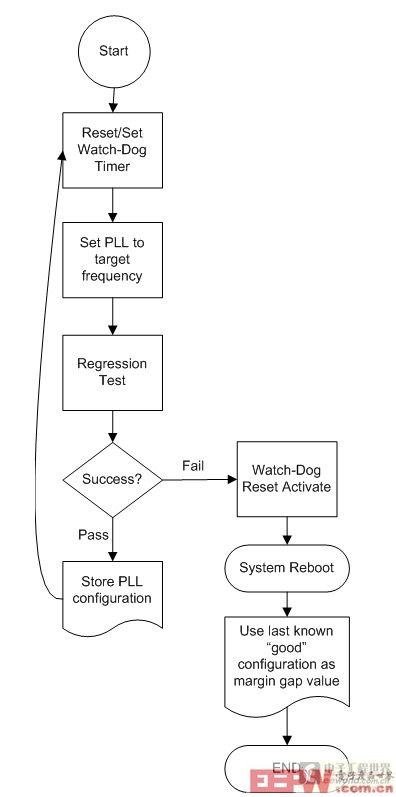

在时钟裕度技术的实施过程中,通过不断调整来修正锁相环时钟源或其他时钟源。图2显示了一个采用时钟裕度技术的简单的锁相环进程的一级方案。管理系统的最佳方法之一,就是采用看门狗计时器,成功完成回归检测后,软件就会重新设置计时器,而系统故障则会导致看门狗计时器超时。反复进行上述工作,重复检测回归计算,存储锁相环频率内容,进程不断重复进行直到出现故障。如前所述,不断趋近总时序预算极限的过程中,可以了解锁相环参数与系统步进变化大小的灵敏度,越接近总时序预算标准极限,步进改变就越小。这样,就要多次循环上述工作,直到取到最后一次成功检测参数为止,超过这个回归检测界限,系统就会出故障。因此最后一个已知的成功回归检测结果就是总时序预算的极限。

图 2:采用时钟裕度技术的简单的锁相环进程。

本文小结

测试时钟裕度性能差的过程,也就是了解总时序预算极限的过程,对了解如何发掘系统的全部潜力很有用。时钟裕度技术有助于找到系统最薄弱的环节,还能不断调节并创建一个匹配的系统,以防止系统超过总时序预算极限发生灾难性后果。总时序预算可以帮助我们明确时钟裕度性能差,估算出产品投入使用后的使用寿命。为了实现上述功能,时钟裕度技术的核心就是可编程的锁相环。通过参考PLL环路编程进程的有关讨论,验证了使用硬件计时器与非易失性存储设备有助于简化管理工作,明确总时序预算极限。

- 利用时钟裕度技术实现系统边界稳定性与早期故障预(01-11)

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)