基于双51单片机的信号处理系统设计

当检测与控制系统处理大量数据和多路信息时,只用一片单片机往往无法满足系统实时性和扩展性要求,且处理时间较长。例如在液面信息采集过程中,单片机要在相等的时间间隔进行A/D转换以及数据处理。由于要实现高通量的液体操作,液体操作平台通常配置多根移液针同时进行液体操作工作,采集多路液面信息。因此这里提出一种基于双单片机的信号处理系统设计方案,该系统采用单片机(AT89S51)作为核心器件,2片AT89S51型单片机作为双核心分担整个检测单元的任务。

1 系统硬件电路设计

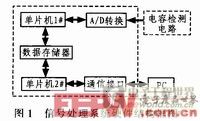

该信号处理系统的总体设计方案为:单片机1定时进行A/D转换,并且将转换结果存入外部数据存储器:单片机2读取数据存储器中的转换结果并且通过串口传递给计算机,同时还负责在系统接收到开始或停止命令之后相应开始或停止单片机1的A/D转换工作。图1为该信号处理系统的硬件结构框图。

根据上述设计方案,该系统硬件分为以下模块:

1.1 A/D转换模块设计

由于AT89S51单片机并没有A/D转换模块,因此在采集系统中需要使用具有A/D转换功能的器件,这里采用ADC0832。ADC0832是美国国家半导体公司生产的一种8位分辨率、双通道A/D转换器。其主要特点如下:输入输出电平与TTL/CMOS相兼容;5 V电源供电时输入电压在0~5 V之间;工作频率为250 kHz,转换时间为32μs;一般功耗仅为15 mW。

A/D转换模块设计采用了ADC0832的以下引脚:引脚1(CS)是片选使能信号端,接单片机AT89S51的P3.4引脚。引脚2(CH0)、引脚3(CH1)是2个模拟量输入通道,由于检测器只使用了一个电容传感器,因此,这里只采用引脚3作为模拟量输入。引脚5(DI)是数据信号输入端,负责选择通道控制。引脚6(DO)是数据信号输出端,负责输出转换后的数据。引脚5和引脚6由于在通信时并不是同时有效,而且与单片机是双向接口,所以在使用过程中将这两引脚连在一起使用,并连接至单片机的P1.1引脚;引脚7(CLK)是芯片时钟输入,接至单片机的P1.0引脚,如图2所示。

1.2 存储模块设计

通过对存储器性能、价格、购买情况等因素的综合考虑,该系统设计采用Cypress公司的CY7C132。该器件是2 Kx8位高速双端口静态读写存储器。两个端口可独立访问存储器内的任意存储单元。该CY7C132有两组对称的信号线,即每个端口都有独立的地址线、数据线和控制线以及通信联络信号位。存取时间为25~55 ns,在非选通时自动处于低功耗状态,异步操作,输入和输出三态,与TTL电平兼容。

CY7C132允许两个CPU同时读取任何存储单元(包括同时读同一地址单元),但不允许同时写或一读一写同一地址单元。双端口RAM中引入了仲裁逻辑(忙逻辑)电路来解决这个问题:当左右两端处理器同时写入或一读一写同一地址单元时,先稳定的地址端口通过仲裁逻辑电路优先读写,同时内部电路使另一个端口的BUSY信号有效,并在内部禁止对方访问,直到本端口操作结束。BUSY信号可以作为中断源指明本次操作非法。需要注意的是:这种方法当CPU发生插入等待时,可能会降低程序效率,不可应用于频繁产生插入中断的场合。

该系统设计采用存取时间为55 ns的CY7C132,从单片机工作速度在μs级,主单片机工作速度在ms级,双方同时读取双口RAM的概率较小,上述冲突解决方案可以满足实际需求。在主从单片机启动工作后,为了防止主单片机的空读,即从单片机的首次写入时间晚于主单片机的首次读入时间,将存储器的首地址设置为起始标志位,通过主单片机读写该为状态决定是否将读取下一位的存储位。

2 具体电路设计

根据上述系统总体结构框图和功能设计,绘制信号处理系统的电路原理图,如图2所示。

单片机的控制或检测工作是通过I/O引脚实现的。单片机1(U1)中,PO和P2引脚以及P3.6与P3.7引脚用来与外部数据存储器CY7C132交换数据;P1.0、P1.1和P3.4引脚是与A/D转换器ADC0832连接,控制A/D转换操作以及读取转换结果:P3.2(外部中断0)引脚与单片机2(V2)的引脚P1.0相互通信。单片机2的I/O引脚的使用情况与单片机1类似。其中特别需要指出的是:单片机2的P1.2引脚连接至CY7C132的BUSY引脚;而P3.0与P3.1是串口通信引脚,连接至MAX232。

CY7C132是双口RAM,但是其任意一端的地址线、数据线以及控制线的连接方法与一般RAM几乎没有区别,2片单片机与CY7C132的地址线和数据线采用相同的连接方法。以单片机1为例进行说明,CY7C132的内部存储空间为2KB,因此,其地址空间为0000H~07FFH。单片机的I/O口要提供11根地址线,除去P0口还需占用P2.0、P2.1、P2.2端。该系统设计仅使用单片机AT89S51的外部RAM,因此不存在片选问题。这里采用线选法,P2.3直接与CY7C132的CS相连。

另外,基于以下原因,单片机1与单片机2使用了不同频率的外部晶振:1)单片机AT89S51支持的频率有限,被选择的晶振频率必须符合要求;2)由于AT89S51使用机器周期作为其工作基准,在使用外部振荡电路的情况下,该单片机是以晶振频率除以12得到的数值作为机器周期,所以在单片机1需要定时器的情况下,晶振频率要便于定时器的设置;3)单片机2需要和计算机进行串口通信,晶振频率要便于串口通信中波特率的设置。因此,单片机1与单片机2的晶振频率分别选择了12 MHz和11.059 2 MHz。

3 系统软件设计

该系统软件设计使用的是汇编语言。汇编语言的优点是:编写的程序存储空间小,运行速度快,程序效率高。另外,汇编语言编写的程序能直接管理和控制硬件设备。汇编语言编写的程序并不能直接为单片机所使用,必须使用编译器编译。本系统使用Keil C5l V7.09评估版。

3.1 单片机主程序

单片机1使用内部RAM的20H.1作为A/D转换标志位,当标志位被置1时,主程序中的A/D转换子程序不会运行;当该标志位被置0时,A/D转换子程序才可以执行。单片机1的主程序执行过程,见图3(a)。单片机2用内部RAM的20H.1作为程序启动标志位,当标志位被置1时,主程序不会运行;当该标志位被置0时,主程序才可以执行。在主程序开始运行后,从外部数据寄存器中读入数据,然后关闭串口中断,通过查询方式向串口写入数据,然后再打开串口中断。单片机2的主程序执行过程,见图3(b)。

- 喷墨打印机在单片机测控系统中的应用(03-01)

- 基于DS18B20的家用温度测量器方案设计(07-01)

- 多芯电缆测试仪的研制 (06-25)

- HDNS2000光学感测芯片在运动检测中的应用(06-25)

- 基于8051单片机的频率测量技术(07-28)

- 基于FPGA的核物理实验定标器的设计与实(07-30)