瞬变光辐射采集系统设计

摘要:介绍一种针对瞬变光辐射信号探测的数据采集系统。该方案以FPGA为控制处理核心,实现了高性能的数据采集。针对特定目标信号,采用变频采样技术,在电路上以变频存储的方式实现,降低了设计难度。采用Altera公司的EPF10K20为设计载体,使用VHDL语言对该采集系统的控制逻辑和时序进行了硬件语言描述。该设计方案占用的FPGA资源少,具有实时性好、可靠性高、集成度高和易于移植等特点。

关键词:瞬变光;变频采样;数据采集;FPGA;先进先出存储器

0 引言

在瞬变光辐射探测系统中,目标信号波形的实时采集至关重要。根据采集到的数据,可以对目标信号的光能量以及频谱分布等各种特征参数进行估计。在传统数据采集系统中,通常采用单片机或DSP作为控制器来控制ADC、存储器和其他外围电路工作。而单片机和DSP的各种功能要靠软件的运行来实现,其执行的效率受到很大限制,软件的运行时间在整个采样时间中占很大的比重。近年来,随着FPGA性能的不断提升,以FPGA为控制核心进行数据采集和存储的应用系统方案得到广泛采纳。FPGA具有单片机和DSP无法比拟优势:FPGA时钟频率高,全部控制逻辑由硬件完成,速度快,效率高;形式灵活,易于移植,可以集成外围控制、译码和接口电路。

本文根据瞬变光辐射探测中强背景、弱目标的特点,设计出以FPGA为控制和处理的核心的数据采集方案。该方案采用背景与信号双重滤波通道,二级程控放大,有效地保证了信号采集质量;同时对目标信号采用变频存储,大大降低了对数据存储与传输的要求,保证了采集过程中有较一致的测量精度。

1 系统组成及工作原理

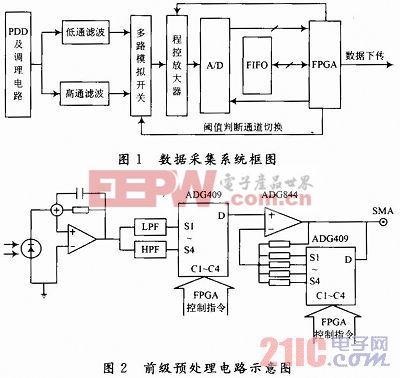

数据采集系统大致可分为三个部分:前级预处理模块,采样存储模块,FPGA控制模块,其中前级预处理模块包括光电转换器件,有源滤波器组,程控放大电路等。整个系统框图如图1所示,光电转换电路将进入系统的光信号通过探测器转化为电流信号,然后经跨阻运算放大器转换为电压信号。系统设计两个滤波通道:背景采用低通滤波,信号采用高通滤波。在起始状态,模拟开关默认选通背景通道,程控放大器设置为背景模式。背景信号经A/D采样后送入FPGA,进行阈值比较。当检测到大于阈值的情况时,FPGA对模拟开关进行通道切换,高通滤波器通道选通,同时程控放大器工作模式选择为信号模式。根据信号前陡后缓的特点,FPGA通过对A/D与FIFO的协同控制,实现数据先密后疏地采集存储。

2.1 前级预处理电路

光电检测电路中,光电探测器直接关系着系统性能的优劣。为了减小由环境电磁辐射所引起的感生电流的影响,器件适宜选择陶瓷封装。另外,探测器的感光面积不能过大,否则会导致暗电流、节电容、上升时间等参数增大,影响探测效果。设计中采用日本滨松公司的S2387硅光二极管,该探测器具有灵敏度高,时间响应快,动态范围大等特点。电路设计采用零偏置模式,无暗电流,二极管噪声主要是分流电阻产生的热噪声,同时具有最佳的精密度和线性度。高低通滤波器采用有源滤波器,反应速度快,滤除谐波效果好,可以动态的补偿无功功率。程控放大器由集成运放与模拟开关组成,通过FPGA控制模拟开关,在运放的输入端接入不同的电阻实现增益的调整。

2.2 采样存储电路

由于目标信号动态范围很大(约为80 dB),因此需要选择宽动态范围的ADC来实现对信号的采集。采用14 b ADC采样幅度变化达4个数量级的动态范围的信号,能满足系统所要求的高探测灵敏度要求。但是由于A/D转换器件都存在精度误差,用高精度的A/D转换元器件当作低精度的A/D转换元器件使用可以减小精度误差。本设计采用ADI公司的16 bAD976A。AD976A低功耗16 b逐次逼近式A/D转换器,转换速度为200 KSPS,可选用内部或是外部的2.5 V参考电源。AD976允许16 b一次并行输出,又可以以两个8 b的形式输出。设计中为节省管脚采用双8 b输出。

为了保证在不同时钟域间准确地传输数据,数据缓存采用异步FIFO。异步FIFO具有高速、可靠性好等特点,能够避免不同时钟间由于相位差异造成数据的误采样。设计中采用的IDT7204是IDT72XX系列中的4 096×9 b的CMOS双口存储缓存芯片。内部读、写指针在先进先出的基础上进行读写,其写时钟W和读时钟R由外部提供;满标志()和空标志()控制数据的溢出和空读,仿真存储器满时写入数据,能方便地进行任意字深和字长的扩展。

3 FPGA控制逻辑设计

数据采集系统以FPGA为核心完成自适应阈值设定,工作模式切换、变频采样存储以及按照接口协议下传数据。数据采样和存储控制流程如图3所示。

3.1 自适应阈值设定

自适应阈值的设定是根据当前背景噪声的大小进行现有阈值进行更新。系统默认的工作状态是背景检测模式,当采集到系统所要求的数据个数后,将这些数据求其有效值后乘以一个加权系数(一般情况下是5~10)作为当前的阈值。系统每隔一段时间给FPGA重新赋阈值。当所采集的数据的幅值连续超过当前阈值设定的次数时,此时系统判定当前的背景信号发生,FPGA控制切换相关的电路,启动相关的电路工作。这样做的目的是防止高能粒子撞击光学镜头或是光罩,瞬间产生超过当前阈值的能量造成误触发。

3.2 变频存储的实现

为了减小信号处理的数据量,根据目标信号的特征,可采用变速率存储技术。尽管所探测的瞬变光辐射信号的最高频率一般在10 kHz左右,根据奈奎斯特采样定理,采样频率只要在20 kHz以上即可以无失真的还原信号,但是所要探测的光辐射信号中有一些关键峰值到达时刻最小不到半个毫秒,高速率采样有助于提高计算峰值到达时刻的精度,同时有利于提高A/D的信噪比。A/D采集系统初始的采样频率为200 kHz,每隔32个采样点,存储频率下降50%。

- 为什么要进行信号调理?(09-30)

- 利用软件工具实现数据的采集和分析 (09-28)

- 高精度微功耗数据采集系统设计与应用(11-03)

- 多通道数据采集系统(11-12)

- 在LabVIEW中驱动数据采集卡的三种方法(04-21)

- 新型智能交通车载信息采集系统研究(09-21)