基于CPCI和光纤接口的数据采集卡设计与实现

摘要:设计了一套基于CPCI总线,PCI9054桥接芯片和可编程逻辑器件(FPGA)的高速数据采集卡。FPGA作为本地主控芯片,根据工控机经PCI9054转发的采集命令,通过光纤接口实现与雷达接收机的通信。采用高速RAM缓存数据,采集的接收机测试数据的分析结果可在工控机上显示,从而实现了对雷达接收机性能的快速测试。该采集卡具有较强的通用性和可扩展性,详细介绍了高速数据采集卡的组成和工作原理、硬件设计。

关键词:光纤接口;CPCI总线;PCI9054;FPGA;雷达接收机测试

随着雷达技术的发展和雷达型号的增多,现代雷达接收机数据处理速度显著提高。因此,在雷达接收机的测试和维护中,对接收机测试系统的数据处理能力、可扩展性等性能要求也在不断提高。传统的雷达接收机测试系统由于专用性强、兼容性差、扩展能力不足,而CPCI总线的通用性、高可靠性和抗震动性使其在雷达信号处理板中得到广泛的应用。同时,由于传输高速雷达信号的需求,光纤在雷达系统中得到了广泛的应用。基于以上分析,本文设计并实现了一种基于光纤接口,使用CPCI总线通信的高速、通用性强的高速数据采集卡。通过实际测试,该采集卡可以很好地完成数据采集等雷达接收机测试的功能,并具有较好的通用性和可扩展性。

1 系统设计

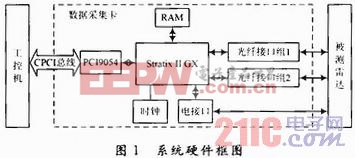

高速数据采集卡主要由StratixⅡGX FPGA、光纤接口、SRAM、PCI9054桥接芯片等构成。本系统设计的目的是应用于雷达数据的采集和分析,为了高速、可靠地传输雷达信号,决定采用光纤作为传输媒介,充分利用光纤传输损耗小、抗干扰能力强、传输速率高等优点。

采用FPGA作为信号采集系统的核心,这种方式最大的优点就是结构灵活,有较强的通用性,适合模块化设计,能够提高效率,同时其开发周期较短,系统容易维护和扩展。图1是该系统的硬件框图。

其工作流程如下:PC机通过CPCI接口将采集命令等送入FPGA,FPGA对命令进行译码,通过光纤接口向雷达接收机发出参数设置命令,然后通过光纤接口接收采集的雷达接收机数据。光纤接口将光信号转换成串行电信号送入FPGA,FPGA对数据进行串/并转换、数据缓冲等所必须的信号处理过程,然后存储到高速RAM中。当计算机发出数据传输命令后,再将数据通过CPCI总线送入计算机进行存储、分析处理和显示等。同时系统还保留了一部分电信号的接口,便于和现有的系统兼容。

2 系统硬件设计

2.1 时钟设计

系统中FPGA的时钟信号由一个125 MHz晶振直接提供,PCI9054的时钟由一个40 MHz晶振提供。高速RAM和光纤接口的时钟信号则是由FPGA通过内部的PLL提供。因为时钟信号是非常敏感的信号,所以要尽量减少反射和串扰等一些问题。在时钟信号线上串接适当的匹配电阻可以有效地减少反射,减少串扰则需要在时钟走线周围留出额外的空间。在本设计中,将时钟线单独放在两个地平面层中间的一层,保证了时钟信号的完整性。

2.2 CPCI接口设计

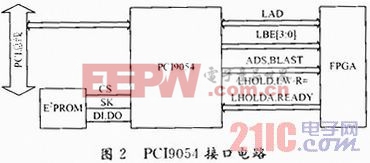

目前,PCI接口的设计有两种方法,一种为使用专用的PCI接口芯片来设计,这种方法相对来说较为简单;另一种方法是利用FPGA进行设计,这种方法比较复杂,开发难度较大。本设计采用第一种方法,即采用PCI9054接口芯片实现PCI总线。

PCI9054芯片适用于通用的32位、33 MHz的局部总线设计。它的本地总线可为三种模式:M模式,C模式和J模式,可利用模式选择引脚加以选择。本设计选用C模式,即32位的地址/数据总线非复用。

PCI9054提供了三种物理总线接口:PCI总线接口、LOCAL总线接口、串行EPROM接口。CPCI接口设计思路是:FPGA通过PCI9054与PCI总线相连,在FPGA内部实现PCI本地端的时序控制。PCI9054芯片内部2个独立DMA通道,可以实现系统数据在PC机内存与数据采集卡之间的高速传输。PCI9054接口电路如图2所示。

CPCI数据采集卡的上电工作流程是:将PCI卡插到工控机插槽中后系统上电自检,此时PCI9054的RST#复位,PCI9054芯片检测E2PROM是否存在,如果存在,PCI9054会根据E2PROM的配置信息初始化其内部寄存器,BIOS根据PCI9054配置寄存器的内容进行系统资源分配,进入系统后安装PCI9054驱动。由以上进程可以看出,E2PROM的配置对于CPCI的正常工作起着重要的作用。

E2PROM配置信息主要包括以下两部分:PCI配置寄存器填写生产商ID号、器件ID号、类码子系统ID号和子系统生产商ID号;本地配置寄存器的配置,即对本地地址空间及其本地总线属性的配置。

2.3 光纤接口设计

光电转换驱动器选用LTP-ST11MB。这款芯片数据速率高达2.5 GHz,兼容光纤通道协议,具有良好的EMI性能。由于该芯片差分输出信号的电平是LVPECL或PECL的,所以要采用AC耦合电路来完成两种电平的转换。耦合电容如果选的太大,将严重减缓信号的传输速度,且由于充放电时问过长,对高速信号的响应将变得很坏;如果太小,将改变线路的阻抗特性,增大衰减。综合考虑,耦合电容的容值在0.01μF比较适当。光纤接口的供电部分要注意的是,发送器和接收器最好采用独立的电源。光纤接口的外围电路配置如图3所示。

- 基于CPCI总线的脉冲信号检测系统设计(01-14)

- 基于CPCI图像采集器的制动片磨损检测系统设计(10-18)

- 基于虚拟仪器的织机纬纱张力测试新方法(05-02)

- 基于虚拟仪器技术的引信软件安全性测试(02-20)

- 实时在线监测,可以轻松实现吗(09-25)

- 基于TPS2491的热插拔保护电路设计(10-10)