基于Pspice的放大器环路的稳定性分析

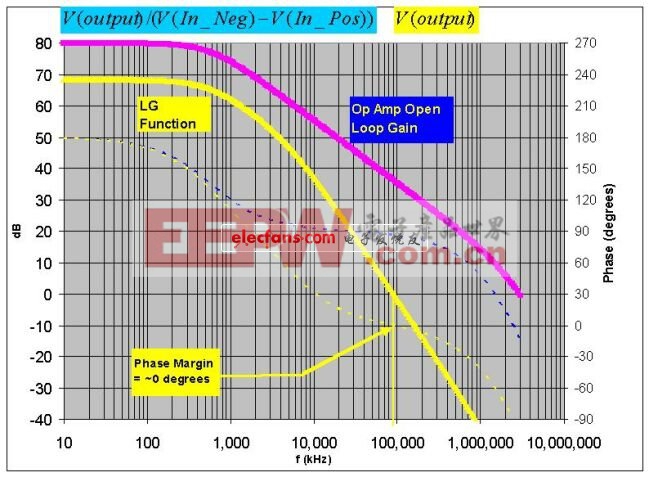

所示。图5中的0o低相位裕度印证了图3中过高的闭环频率响应峰值。为确保电路的稳定性,对应的品质因数即相位裕度应大于45o。

图5:开环曲线表明相位裕度不足。

请注意:在频率响应仿真开始之前,请确保将输入电流源(取代光电二极管)设定为“AC 0”;显示结果需将CF设为0pF;图5中幅度用实线表示,相位角用虚线表示;当相位裕度为0dB时,相位裕度对应LG函数的相位角。

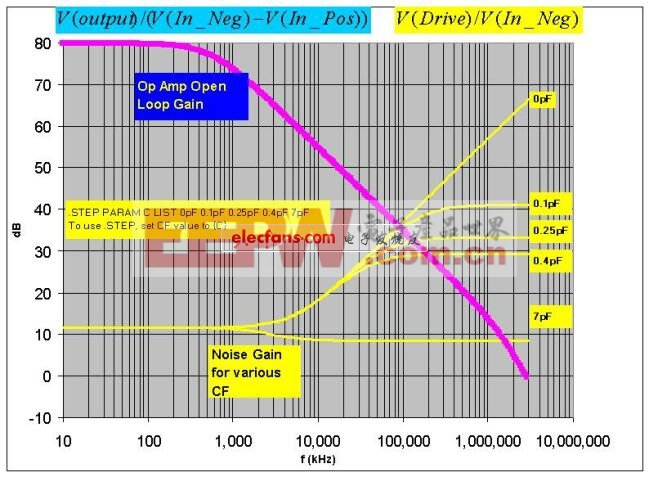

如图6所示,为找到合适的补偿电容值来改善相位裕度,我们可以将针对不同的CF值(图4电路)的噪声增益曲线和LMH6629开环增益曲线放在一起。噪声增益为V(Drive)/V(In_Neg)。请注意LG的仿真低频值要大于0dB,因为LMH6629的宏模型还包括了其差分输入电阻。

图6:CF最优化噪声增益曲线。

大部分Pspice仿真器都允许使用图6所示的“.STEP PARAM”语句来进行多级仿真并显示迭加的结果。其它仿真器可能有专用命令来实现此类同步仿真功能。最优CF值在噪声增益函数与LMH6629的开环增益曲线相交频率处给噪声增益函数设置了一个极点。由图6可知,在本例中,CF=0.25pF。

大于0.25pF的更高CF值将会带来带宽损失,相应地,若CF低于0.25pF,相位裕度又将不足。如果CF足够高(本例中是7pF),噪声增益曲线有可能在低于20dB处与开环曲线相交。20dB是LMH6629的最小稳定增益。这种情况下电路可能将不再稳定或者放大器可能出现过高频率响应峰值。因此必须有一个稳定范围和最优值。

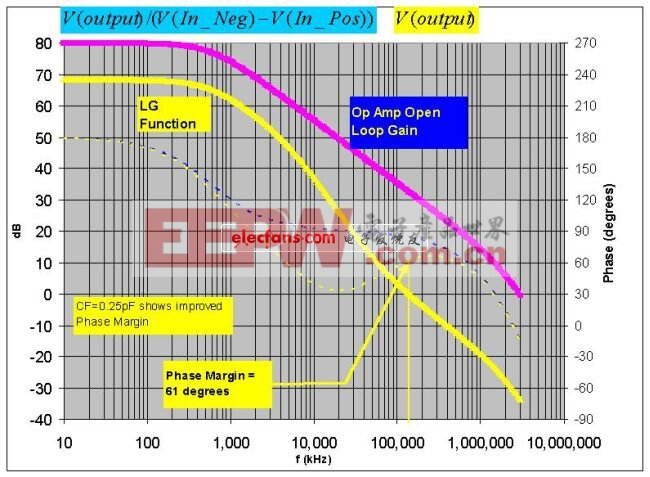

图7所示的是当CF=0.25pF时,频率函数LG的结果曲线。在没有CF的情况下,相位裕度从原来的0o增加到61o。

图7:开环曲线绘制验证CF令相位裕度得以改善。

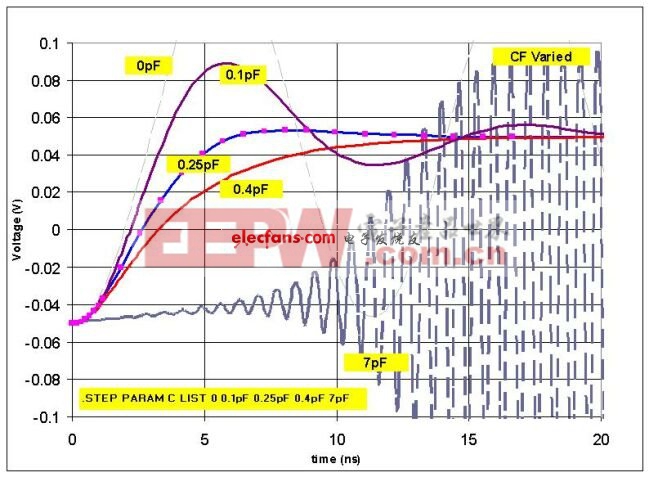

找到最优CF值后,可以重新查看初始的闭环配置(没有大电感和电容加入到LG和NG的研究中),在使用最优CF值(此时是0.25pF)的情况下可以得到阶跃响应。图8显示了面向不同CF的响应曲线,证实了CF值不论是偏大或是偏小,都会造成系统的不稳定,或是振铃时间和稳定时间的延长;而最优CF值可以在最小振铃下实现非常好的阶跃响应。显然,无论CF取值0pF还是7pF,电路都非常地不稳定。这表明7pF时的振荡频率远高于0pF时的振荡频率,并不是因为噪声增益与放大器开环增益曲线的交接频率较高(如图6所预测的那样)。

图8:不同CF对应的闭环阶跃响应。

实际考虑和实验结果比较

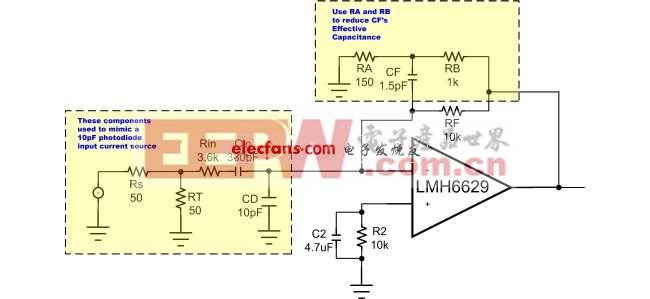

利用基于Pspice的分析方法来研究合适的补偿值,并通过仿真找到最佳响应时的参数值后,接下来就是在实验台上验证仿真结果。图9为一个实验台的验证设置示意图。

图9:TIA补偿实验台验证设置。

以下是图9实验台设置的一些要点。

低电容值和实验台优化:为降低有效电容值,可以将RA、RB串在一起并与CF邻接,这样可以用一个市场上容易找到的电容(>1pF)来获取皮法以下的电容值,而该值很难直接获得。只要RB RF,该电路即可将CF的等效电容值降低1+ RB/RA倍。该方法可以得到一个0.20pF的等效电容,选用这样的设置是因为0.25pF的仿真值会产生过阻尼实验台响应。物理电路板会存在一定的寄生电感和电容,它们可以被最小化,但是不能完全降低到0。因此,人们希望通过实验台测试来促进对仿真结果的优化,特别是在处理皮法级以下的标称值时。等效电容为0.20pF时,检测到的带宽为70MHz;而当等效电容为0.25pF时,带宽下降至55MHz。

等效光电二极管实验台设置:为便于测试,所示的(Rin, Cin以及CD)前端配置允许使用标准的50?实验室设备来模拟光电二极管的性能。这里CD(假设为光电二极管电容)被设定为10pF。

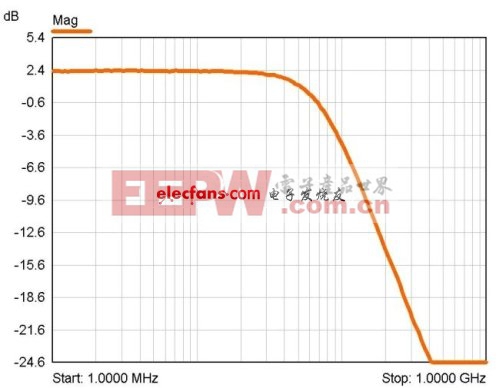

图10:CF_eq=0.2pF时测定的频率响应。

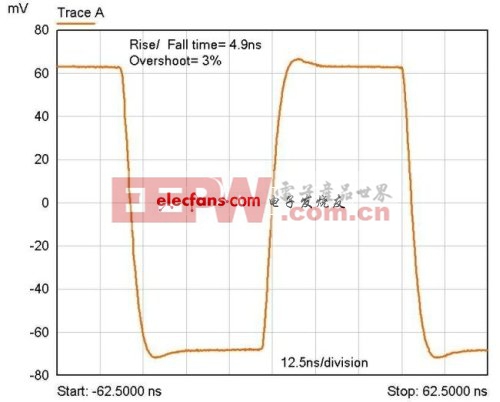

图10和图11分别显示了使用50?源和输出端负载得到的频率响应和阶跃响应结果。如图所示,-3dB带宽时,频率接近70MHz,没有峰值。阶跃响应曲线在上升时间和下降时间与频率响应相匹配,图中显示了最小过冲值,没有振铃,从而可以确定电路已被正确地补偿。为了对仿真作进一步确认,实验台测试验证了在没有补偿电容时出现的大峰值以及10pF电容跨接RF时所产生的全振荡过程。

图11:CF_eq=0.2pF时测定的阶跃响应。

测量结果被证实是可靠的,充分补偿了70MHz的带宽,符合方程式1中的理论值,该方程式中CIN为总反向输入电容(包括二极管和运算放大器)。

通过断开环路,并借助Pspice的迭代函数(即阶跃函数),人们就能在很短的时间内更好地寻找最优补偿方法,实现环路的稳定性。本文的例子充分说明了该方法的简便和灵活性。当然,本文所用的运算放大器的宏模型必须对器件精确建模(包括输入阶段的寄生效应),否则获得的结果就有可能远远偏离实际值。这个例子所演示的技术并非仅适用于TIA电路(这只是选取出来的一个具有代表性的例子),

- 利用Pspice通用测试电路实现关键参数的模拟(上)(01-30)

- 利用Pspice通用测试电路实现关键参数的模拟(下)(01-30)

- 利用Pspice通用测试电路实现关键参数的模拟(下)(06-04)

- 利用Pspice通用测试电路实现关键参数的模拟(上)(06-04)

- 利用Pspice分析放大器环路的稳定性(08-10)

- 面向宽带数据应用的SiGe跟踪保持放大器(10-28)