基于MPEG-4的嵌入式多媒体监控系统中压缩/解压卡的

1 MPEG-4 标准及其在多媒体监控系统中的应用

多媒体监控系统是多媒体技术在安防领域的新应用。音视频压缩技术是多媒体监控系统中的关键技术。在数字多媒体压缩领域内有很多国际标准,如ISO/ITU-T 技术委员会下的JPEG 标准,CCITT制定的H. 263标准,以及著名的MPEG标准等。

MPEG-4标准于2000年10月公布。MPEG-4 标准的主要特点是对图像中的内容进行编码, 其核心是基于内容的尺度可变性(Content - basedscalability) 。内容尺度可变性意味着给图像中的各个对象分配优先级。其中,比较重要的对象用较高的空间和(或) 时间分辨力表示。对甚低比特率应用来说,尺度可变性是一个关键的因素,因为它提供了自适应可用资源的能力。例如,这个功能允许使用者规定:对具有较高优先级的对象以可接受的质量显示,第二优先级的对象则以较低的质量显示,而其余内容(对象) 则不显示。对于监控系统来说,在绝大部分时间内,监视画面的背景都保持不变,因此在要求低比特率时,对于监视画面的背景部分可以以较低的质量显示,且不会影响整个画面的效果。本系统采用MPEG

- 4 压缩标准,在实现上选择硬压缩和硬解压, 所用的压缩解压芯片为VWEB公司的VW2010 芯片。

2 硬件设计原理

2.1 VW2010 芯片的主要特点

VW2010是VWEB公司开发的实时MPEG-4音视频压缩/ 解压芯片(CODEC) 。该芯片具有以下主要特点:

(1) 单片集成3 个信号处理/ 控制单元,包括一个视频编码(压缩) 器、一个视频解码(解压) 器和一个片内CPU(内部扩展一个音频编码DSP、一个音频解码DSP、一个多路复合单元和一个多路解复合单元) 。

(2) 为了达到可编程、高性能和低功耗,每个信号处理/ 控制单元都是由一个RISC处理器和专用的硬件加速器构成,视频编、解码器内部还集成一个专用的SDRAM。

(3) 在系统上电/ 复位时,视频编、解码器的固件程序从外部主机(host )载入各自专用的SDRAM;片内CPU的固件程序载入VW2010外挂的SDRAM。

(4) 芯片主机接口采用标准PCI 接口。符合PCI局部总线规范2. 2 。

(5) 为了使编、解码性能达到最佳,VW2010内部集成了一个双通道DMAC。系统host直接通过主机接口对VW2010 进行控制,MPEG流数据则采用DMA方式传输。

(6) 提供了与PHILIPS公司兼容的I2C总线,方便对外围芯片的控制。

2.2 基于VW2010 的压缩/ 解压卡硬件设计原理

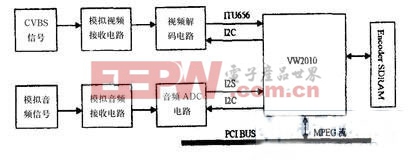

压缩卡的原理框图如图1所示。CVBS信号先经过视频接收电路进行前端处理,包括阻抗匹配、限幅和钳位,然后通过视频解码电路产生符合VW2010视频接口标准的ITU656信号。视频解码电路的核心是一个视频解码芯片,解码芯片对CVBS信号进行A/ D转换和编码,产生ITU656 标准的并行数字电视信号。高档的视频解码器还支持图像尺寸缩放( scaling) 和帧提取(decimating) 功能,如PHILIPS 公司的SAA7114 、SAA7115 以及Rockwell 公司的BT829A 等。由于VW2010的视频输入为ITU656/D1 格式,所以只需要选择具有基本A/D 转换和编码功能的视频解码芯片如SAA7113 即可。

图1 压缩卡原理图

模拟音频信号先经过模拟音频接收电路进行前端处理,然后通过音频ADC 产生符合VW2010音频接口标准的I2S 信号。VW2010是压缩卡的核心处理芯片,除了完成音视频编码外,还提供对解码器和ADC 的控制(通过I2C 总线) ,编码产生的MPEG流则通过芯片内部集成的PCI 接口输出。

解压是压缩的逆过程,基本原理类似,限于篇幅,不再赘述。

3 Linux 下V W2010 设备驱动程序设计

3.1 VW2010 与host 的通信机制

VW2010提供了三种用于同host 通信的机制: 直接访问内部寄存器、共享存储区( sharedmemory) 和DMA。VW2010允许host 直接访问其内部寄存器和外部存储单元,寄存器方式主要用于调试目的和下载固件程序; DMA 方式则负责VW2010 芯片和应用缓冲区之间的数据传输(如MPEG流数据) ;共享存储区机制是设备驱动程序和VW2010 间的主要通信方式。

3.1.1 共享存储区(shared memory)

VW2010 采用共享存储区机制接收host 的命令并返回命令执行结果。用于host 到VW2010 通信的共享存储区(以下简称SM-PC2VW) 位于en-coder SDRAM 中地址3F1800 处,共128 字节; 用于VW2010到host 通信的共享存储区(以下简称SM-VW2PC) 位于encoder SDRAM 中地址3F1880 处,共128 字节。

SM_PC2VW 的格式如表1 所示。表中,CMD 为命令码, 分别是: 读数据(CMD=1) 、发IOCTL 码(CMD=2) 、写数据(CMD=3) 、打开命令(CMD = 4) 和关闭命令(CMD=5) ; Int Flag为中断标识, Int Flag 为1 ,则VW2010 执行完CMD 定义的任务后将产生一个中断,为0 则不产生;Device Handle 由打开命令从firmware 中获得; 当CMD不同

- VoIP视频流质量的测量和监控的实例(11-07)

- MPEG测试系统应用指南(01-27)

- 泰克展出三网融合下的数字视频解决方案(03-01)

- MPEG-2码流分析仪的整体设计与软件实现(01-12)

- 基于GPRS的配变监控系统的设计与实现(06-18)

- 流媒体在网络视频监控系统中的应用 (10-07)