通用电路板自动测试系统方案设计与实现

号一般不作为关键测试信号,若需测试时可按高频信号进行采集。其中电源信号和电平变换信号均可视为直流信号来采集,用AD7864 完成采集。而脉冲数字信号的频率较高,动辄就几十兆赫兹甚至上百兆赫兹,需要用高速的AD(本系统中用的是AT84AD331) 来进行采集,并且需要对频率进行测量。因此本系统信号采集分为低频和高频两个部分,下面分别叙述:

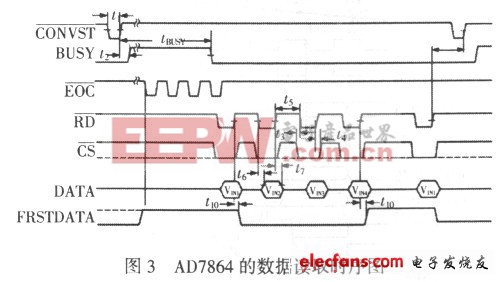

(1)低频部分。本部分主要采集的是电源信号和电平变换信号,采用AD7864 作为采集芯片。AD7864 具有片内时钟、读写允许逻辑、多种通道选择方式以及内部精确的2。5 V 参考电压,这使得其与高速处理器的接口变得非常简单。AD7864 转换后的数据读取采用转换后读取数据的方式,其读取时序见图3。

采集到的数据为D3~D11 共12 位,需根据采集到的数据来计算电压值,计算公式如下:

当D11 位为3 时,电压为正值,计算公式为:

当D11 位为1 时,电压为负值,计算公式为:

以上两式中D 为读取的12 位数据,FSR 为AD7864 的测量范围,本例中为23 V(测量范围为V)。

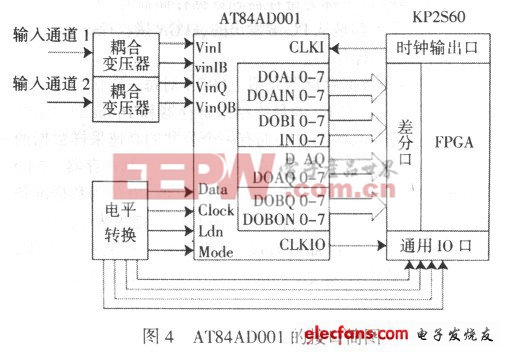

(2)高频部分。主要是对脉冲数字信号的采集,包括频率测量和信号采集两个部分。脉冲数字信号的频率是确定电路板是否工作正常的重要参数,因此确定脉冲信号的频率是否正常是本测试系统的必要工作。本系统是将待测信号接入FPGA 与53MHz 的高精度时钟同时开始计数,一段时间后,通过两个信号的计数值来计算脉冲信号频率的。信号采集是以AT84AD331 作为采集芯片。AT84AD331 与EP2S63 的连接见图4。

AT84AD331 可以配置成I 路和Q 路单独使用,此时可以同时采集两路信号,最高采样率为1 Gs/s;也可以配置成I 和Q 路的交错采样,此时只能采集1 路信号,等效采样率为2 Gs/s,使用时可以根据需要对该芯片进行在线配置。FPGA 对AT84AD331数据读取时序见图5。

由于AT84AD331 输入信号为差分信号,且信号峰峰值要求不超过533 mV。电路板上的待测信号都是单端的并且峰峰值一般在4 V~5 V 之间。本系统中采用了13∶1 的变压器耦合输入方式,可以完成单端信号到差分信号的转换,并且使信号电压满足要求。

在FPGA 内部完成对LVDS 信号的读取、组合、排序以及存储等操作。一般情况下存储的采样点的值在1 333 以内,然后对这些采样点的值进行计算,可以得到实际电压值,计算公式如下:

2.3 数据传输和控制协议

系统中待测信号较多,低频和高频部分分别是32 个,而数据采集芯片都只有一个,各个信号都是由FPGA 控制模拟开关分时地进行采集的。为使各个通道的数据存储、传输和控制有序地进行,在FPGA 中为每一个信号都设置了工作状态控制模块和数据存储模块(以下称为寄存器和数据存储器)。本系统中所有控制过程的命令都是从PC 端发出的,FPGA 接收控制指令后,按指令进行相应的操作。

(1)寄存器和数据存储器介绍。FPGA 对每一路信号都设有5 bit 的控制寄存器、12 bit 的最终结果寄存器和16 bit 的原始数据存储器。此外在高频部分还拥有一个公共的高速采样数据的存储器,大小为1 kB,及其对应的一个8 bit 的控制寄存器。5 bit的控制寄存器每个通道只设有一个,该寄存器D3 位为数据准备好标志(1 有效),其余4 位为控制位,各位的功能见表1,每一位都是1 为肯定,每一位都可通过PC 端发来的控制指令更改,FPGA 只能向D3 位写1 ,表示数据已经准备好。上电或复位后该寄存器值为33333B。

表1 5bit控制寄存器的位功能

12 bit 的最终结果寄存器每个通道也只设有一个,该寄存器的值是向PC 机发送的最终结果。该寄存器的数据在低频和高频部分,存放的数据不同:低频部分存放的是13 次采样结果的平均值,高频部分存放的是计算后的频率值。

16 bit 的原始数据存储器,其低频和高频部分的数量是不相同的:高频部分一般是2 个,分别用来存放标准和待测时钟的计数值;低频部分为13 个,用来存放13 个采样点的值,12 bit 的最终结果寄存器的值是根据这13 个数据的平均值。

高速采样数据存储器是高频部分的32 路共有的,由于波形采样的数据量比较大,本系统设计时在同一时刻只允许采样1 路信号,采样点数可以设定(最多为1 K),待这些数据全部发送出后,才可以开始下一次采集。对应的控制寄存器的位功能见表2。

表2 高速采样控制寄存器的位功能

其中D7~D4 为数据采集的点数设置,3333B 表示64 个,1111 表示1 324 个,步进为64。D3~D1 为数据抽取的间隔设置,333 表示抽取间隔为3,全部数据有效;111 表示抽取间隔为28,即每隔28 个点抽取一个点,步进为4。设置这几位的目的是为了适应信号频率的要求

- 通用电路板自动测试系统的设计与实现(10-03)

- 基于声表面波器件的无线远距识别系统方案设计与实现(10-22)

- 基于CTMU的精确激光测距方案设计(04-23)

- 基于LabVIEW的海洋环境多物理场测量系统的方案设计(10-02)

- 便携式岩土热物性测试仪方案设计(09-15)

- 脉搏血氧测量方案设计(08-19)