Launch-off-shift实时测试

在实时扫描测试期间,必须同时考虑虚假路径和多循环路径。扫描可能会直接将扫描单元装载到一种正常工作下不可能的电路状态。因此,可能虚假路径或多循环路径在实时扫描测试期间是活动的。如果实时扫描测试由于这些路径而失败,则可能错误地废弃那些功能正常的器件,从而导致良率损失。

为避免这种损失,工程师们经常会在时基仿真和程序测试器集成期间对虚假路径和多循环路径进行测试,而且他们一般以手工完成这些工作。

所幸的是,ATPG 工具已经增加了自动化能力,现在它们可以直接读取标准的 SDC 文件,并提取出除去时序异常路径信息(参考文献 9)。利用这种自动化功能,如果某个测试沿一个在 ATPG 期间检测到的虚假路径或多循环路径传播信号,则捕捉扫描单元将捕获到一

个未知的 X 值。

基带芯片案例研究

Metalink 是一家设计无线和有线宽带通信芯片的公司,它需要为符合 WLANPlus 802.11n 草案的无线 LAN 技术(该技术最适合用于网络家庭娱乐环境)开发一种有效的测试策略。该公司的 WLANPlus 系列包括 MtW8171 基带器件和 MtW8151 RFIC。MtW8171 基带芯片采用 90 nm 低功耗工艺制造,并实现了完全的实时扫描测试能力。对这款器件,实时扫描实现的同时采用了 LOS 和全面跳变样本。

为了减少覆盖跳变故障所需增加的样本数,我们采用 Mentor Graphics 的嵌入式决定性测试(Embedded Deterministic Test)技术实现了逻辑压缩。从收到芯片直到所有构建的样本均启动并实时运行,该芯片的整个扫描过程只花了两天时间。

我们在实验中比较了全面跳变样本和 LOS 覆盖的差异。我们采取定义可用特定时钟顺序的做法,生成了初始样本。

表 1 是跳变样本生成的结果。开始时,LOS 样本有 78.57% 的测试覆盖率,与之相比,全面样本为 71.38%。因此,看来 LOS 可以多测出 >7% 的故障。接下来,我们考虑虚假路径与多循环路径,因为预计这些路径在工作时钟速率下无法运行。

考虑了虚假路径和多循环路径(MCP)后,LOS 和全面覆盖率分别降低到 72.88% 和 69.55%。因此,初始 LOS 检测报告的错误中有 5.69% 是虚假路径和 MCP。同样,1.83% 的全面检测是源于虚假路径和 MCP。根据这些结果,我们得出结论,LOS 样本的测试覆盖率中,相当大一部分优势来源于虚假路径和 MCP 测试。

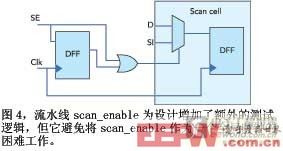

这些结果表明,当考虑了 LOS 样本实际的虚假路径和多循环路径时,就降低了过度测试的风险。于是,LOS 可以成为实时测试的一种有吸引力的 ATPG 方案。在相近覆盖率下,样本生成时间和样本数量都远远少于全面样本。流水线 scan_enable 与虚假路径和多循环路径的结合,解决了 LOS 样本中最常见的问题。全面样本仍可应用于结束(top-off)覆盖,因为 LOS 样本无法检测出某些缺陷。

下一个是什么?

制造商们正在继续寻找提高实时扫描测试效率的方法。一种方法称为“timing-aware”(时序感知)ATPG(参考文献 10),目的是降低延迟失真。它试图沿着尽可能缓慢的一条路径(最小弛滞)传播跳变,从而测试出每个缺陷。用这种技术,实时测试样本集更可能检测出小的缺陷,而用普通跳变测试集时则可能漏检。

实时扫描测试的另一种新方法是在触发循环前采用一系列实时跳变。这种“BurstMode”(突发模式)ATPG(参考文献 11)有助于使实时时钟脉冲更像工作时的频率脉冲。它减轻了由于触发时实时时钟突发脉冲造成的电压降,并能在正常的跳变测试期间完成捕捉。这两种技术都应考虑对虚假路径与多循环路径的处理,以避免过度测试的风险。

与此同时,像流水线 scan_enable 这类技术也使 LOS 更为可行,使用户能够在两种跳变样本类型之间进行权衡,并确定自己的最佳解决方案。全面样本有较少的逻辑插入,以及较少的非功能性路径测试,而 LOS 样本有更快的样本生成和更少的样本。对于那些有兴趣检测所有类型缺陷(包括非功能性缺陷)的公司,LOS 方案可能也有吸引力。所幸的是,ATPG 工具通过设计流程中常用的 SDC 文件来处理虚假路径和多循环路径,从而减轻了对过度测试的担忧。

参考文献

1. Benayahu, N., et. al., “Scan basics,” sidebar accompanying this article.

2. Saxena, J., et. al., “Scan-Based Transition Fault Testing: Implementation and Low Cost Test Challenges” Proceedings of the International Test Conference 2002, IEEE Computer Society Press.

3. Bailey B., et. al., “Test Methodology for Motorola’s High Performance e500 Core Based on Power-PC Instruction Set Architecture,” Proceedings of the International Test Conference 2002, IEEE Computer Society Press.

4. Boyer, J., and R. Press, “Easily

- 实时测试技术的演变进程(06-29)

- 简述实时测试的演变(12-26)

- 实时测试技术简介以及其演变过程(09-18)

- 实时测试的演变发展(11-23)

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)